## University of California at Berkeley College of Engineering Department of Electrical Engineering and Computer Science

EECS 150 D. E. Culler Fall 2007

## Homework #5: Memory and Protocols Assigned 10/4/2007, Due 10/12/2007 at 2 PM

**Problem 1**: Draw a state transition diagram (STD) for a Moore machine that has

$$\label{eq:continuous_problem} \begin{split} & \text{input } i \in \{\,\texttt{q, r, w, z}\,\}, \\ & \text{output } o \in \{\,\texttt{0, 1}\,\} \end{split}$$

and recognizes instances of the pattern rrz.

For example, input

qrwzrrzrzrrzw

produces the output

00000010000010.

Draw a STD for an equivalent Mealy machine.

**Problem 2:** Modify your state diagram to recognize patterns of the form r+z, where r+ means a sequence of one or more r's. What is the output for the input in problem 1?

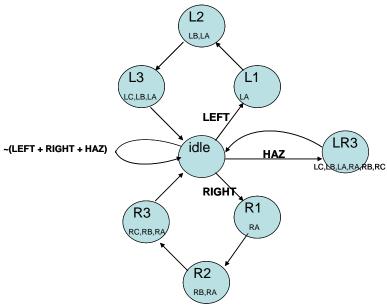

**Problem 3:** The old T-bird had a series of three taillights on either side (LC|LB|LA and RA|RB|RC) that lit up from the center our when you turned on the blinker. Here's a state transition diagram for the controller. Give the corresponding symbolic state transition table.

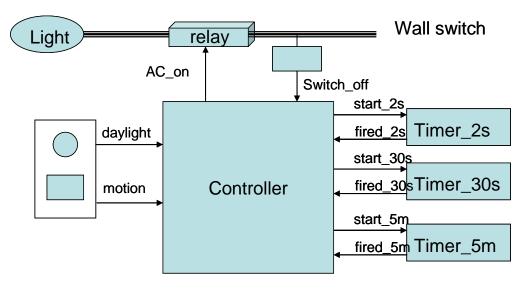

**Problem 4.** In this problem you will design a (now familiar) motion-based light controller shown in the diagram below. The wall switch is normally left in the ON position, supplying power to the controller and the light. The normal behavior of this controller is to turn the light ON for 30 seconds after motion is detected, but only if it is dark out. In addition, there is an override mode where if the switch is turned OFF and back ON within 2 seconds it turns the light on for 5 minutes, regardless of daylight or motion. Override can occur while the light is ON, either due to motion or test.

Your controller has two digital inputs based on the photocell and passive infrared sensors: **daylight** and **motion.** In addition, it has a circuit that detects when the switch is turned off and provides the input **Switch\_off**. (The controller has a backup capacitor so it can run for a while with the switch off.) It has an output **AC\_on** that controls a relay to actually turn the light on and off. It has three preset timers, each with a **start** control point and a **fired** signal. The start signal for a timer should be asserted for one cycle to start the timer. Each time it is pulsed it will reset the timer.

- **a**. Give the symbolic state transition diagram for a Moore FSM controller. (This should be a clear high level specification of the behavior.)

- **b**. Give a symbolic state transition table. (This should be 1-1 with your STD. It should not contain the specific concrete encodings of the states. It must cover all the possible inputs in each state using appropriate don't-cares to make it concise.)

- **c.** Implement your controller as a behavioral verilog module. The structure of the code should closely reflect your STD and STT. Use the same symbolic state names with parameter statement to give the concrete encodings. It should have two ALWAYS blocks. The combinational block should have a case statement with an arm for each state.

## Problem 5

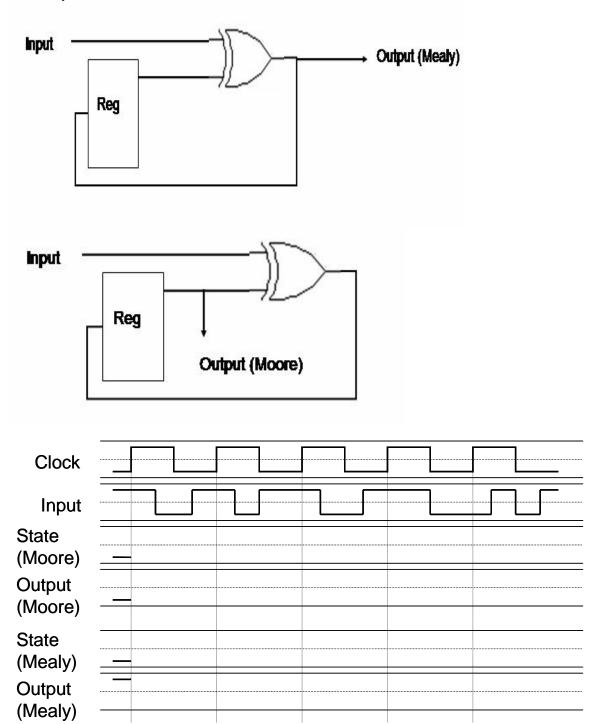

a) Given the following Mealy and Moore circuit representations, complete the timing diagram given the input. The clock has a period of 8 ns and the register has a clk-to-Q delay of 2 ns and the XOR has a delay of 1 ns.

b) Explain the implications of using a Moore versus Mealy representation of the outputs for this circuit.

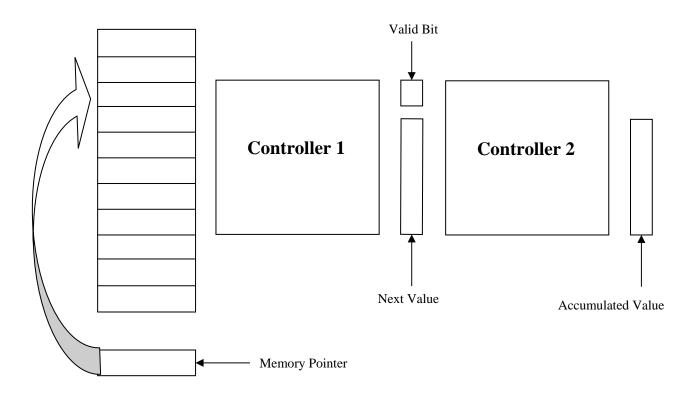

**Problem 6.** Draw the State Transition Diagrams for the controllers below. Controller 1 is the data producer; it streams a sequence of values to the shared, single word buffer. Concretely, it reads the value from the memory location pointed to by the memory pointer, places it in the next value register, and sets the valid bit to inform the consumer that the shared buffer is full. It increments the memory pointer before reading the next word. Controller 2 is the data consumer; it takes the value from the next value register when valid, clears the valid bit, accumulates the value and places it in the accumulated value register. The true controllers operate independently and run and potentially different rates. The producer cannot overwrite the buffer until it has been emptied, and the consumer cannot read it until it is full. Be careful to design the FSM's such that memory locations are not added in multiple times in a row and that values are not lost.

Note that this problem is a little bit open ended. You will need to specify the inputs and outputs of your two cooperating state machines, as well as determining the symbolic states and the functional behavior.