## **JNIVERSITY OF CALIFORNIA AT BERKELEY**

ERKELEY • DAVIS • IRVINE • LOS ANGELES • RIVERSIDE • SAN DIEGO • SAN FRANCISCO

Department of Electrical Engineering and Computer Sciences

SANTA BARBARA • SANTA CRUZ CS 150 - Spring 1998 Prof. A. R. Newton Prof. K. Pister

| TOTAL | /100 |

|-------|------|

| (3)   | /40  |

| (2)   | /30  |

| (1)   | /30  |

## **Ouiz 2 Solutions**

| OTAL | /100 |

|------|------|

|      |      |

Room 10 Evans Hall, 2:10pm Tuesday April 7<sup>th</sup>

(Open Katz only, Calculators OK, 1hr 20mins)

Include all final answers in locations indicated on these pages and in pen. Use space provided for all working. If necessary, attach additional sheets by staple at the end. BE SURE TO WRITE YOUR NAME ON EVERY SHEET.

1. (30pts) (a) A digital system is required to amplify a binary-encoded audio signal. The user should be able to control the signal amplitude from minimum to maximum in 100 increments. What is the minimum number of binary bits required to encode the user-specified amplitude?

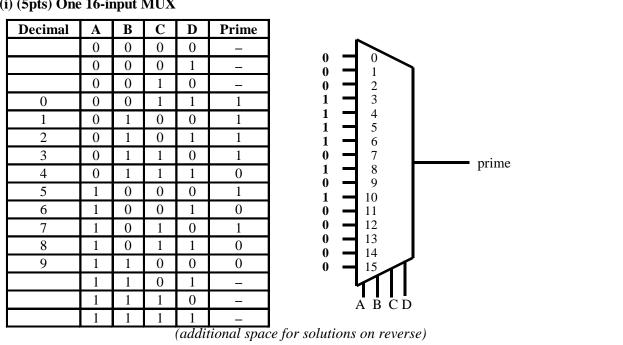

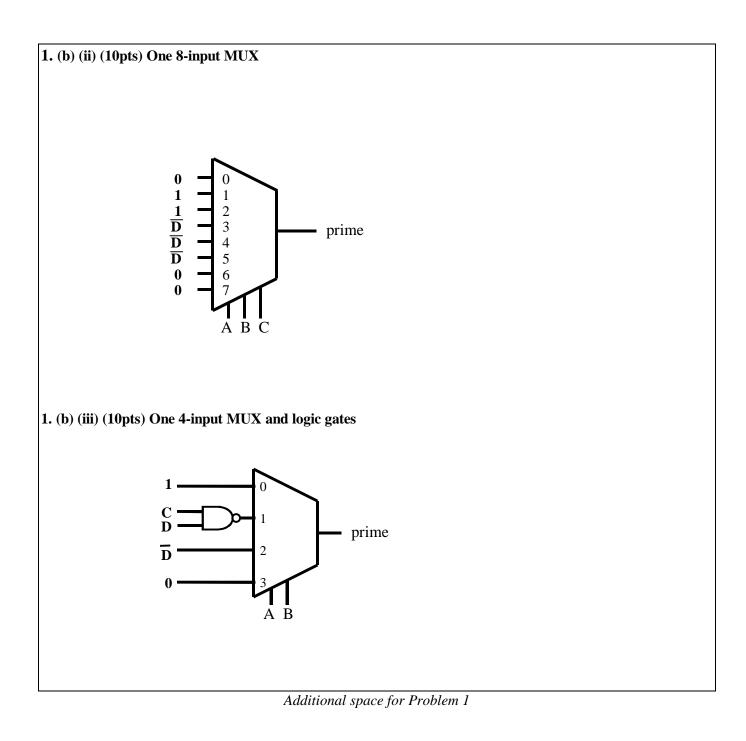

(b) Excess-3 code (Katz page 499) is a variation of binary-coded decimal (BCD) code. Each decimal digit is represented by a 4-bit code that is three more than the associated BCD code. For example,  $0_{10}$  is encoded in excess-3 as  $0011_2$ ,  $1_{10}$  is encoded in excess-3 as  $0100_2$ , etc. Design a **single-output combinational logic circuit** that outputs a 1 when the input to the circuit in 4-bit excess-3 code is a prime number. For all other (non-prime) legal 4-bit excess-3 numbers applied to the inputs, the output is a 0. Assume complement inputs are available and implement the circuit using:

- One **16-input**, four control-line multiplexer only. (i)

- (ii) One 8-input, three control-line multiplexer only.

- (iii) One 4-input, two control-line multiplexer and a minimum number of simple logic gates (INV, NAND, NOR, AND, OR, XOR, XNOR)

## 1. (a) (5pts)

Number of bits =  $_2^6$ =64 and  $2^7$ =128 so seven bits are required\_\_\_\_\_

## 1. (b) (i) (5pts) One 16-input MUX

| me: |

|-----|

| me: |

- (2) (30 points)

- (a) What is the better way to implement arithmetic in a binary computer: one's-complement or two's-complement? Why? Include all of the arguments you can think of for and against your answer.

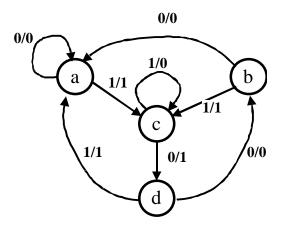

- (b) Does the state-machine opposite have any **equivalent states**? If so, **which states are equivalent**? Show all working.

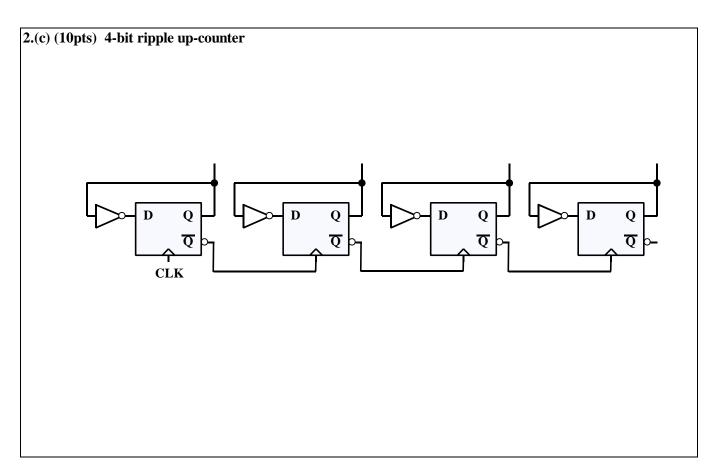

- (c) Design a **4-bit ripple up-counter using positive edgetriggered D flip flops** and a minimum number of combinational logic gates. Show the schematic diagram.

| (a) (10pts) One's or two's com  | plement? Why?                                                         |

|---------------------------------|-----------------------------------------------------------------------|

| 2's complement                  |                                                                       |

|                                 | and subtraction (sum of -ve #s) (can be done in one byte-serial pass) |

|                                 | for 0                                                                 |

| must add 1 for making           | g -ve #s                                                              |

|                                 |                                                                       |

|                                 |                                                                       |

|                                 |                                                                       |

|                                 |                                                                       |

|                                 |                                                                       |

|                                 | (continue on reverse if necessary)                                    |

| (b) (10pts)                     |                                                                       |

| Equivalent states: <u>a</u> = b |                                                                       |

| Equivalent states: <u>a</u> – D |                                                                       |

|                                 |                                                                       |

|                                 |                                                                       |

|                                 | b a a a c a c a c a c a c a c a c a c a                               |

|                                 | c X X                                                                 |

|                                 |                                                                       |

|                                 | a b c                                                                 |

|                                 | (additional space for solutions on reverse)                           |

Additional space for Problem 2

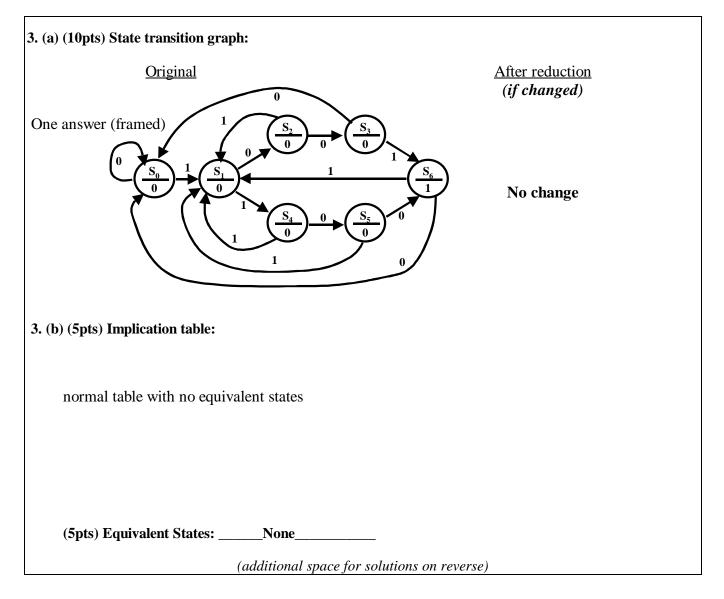

**3.** (40 pts) Design a Moore machine that detects the number 9<sub>10</sub> encoded in binary (1001<sub>2</sub>) and in excess-3 (1100<sub>2</sub>). The machine should reset after each detection (i.e. overlapping sequences are ignored). Sample input (X) and output (Z) sequences are given below:

X=1001100011001... Z=0001000000010...

- (a) Draw a state transition diagram for the Moore machine.

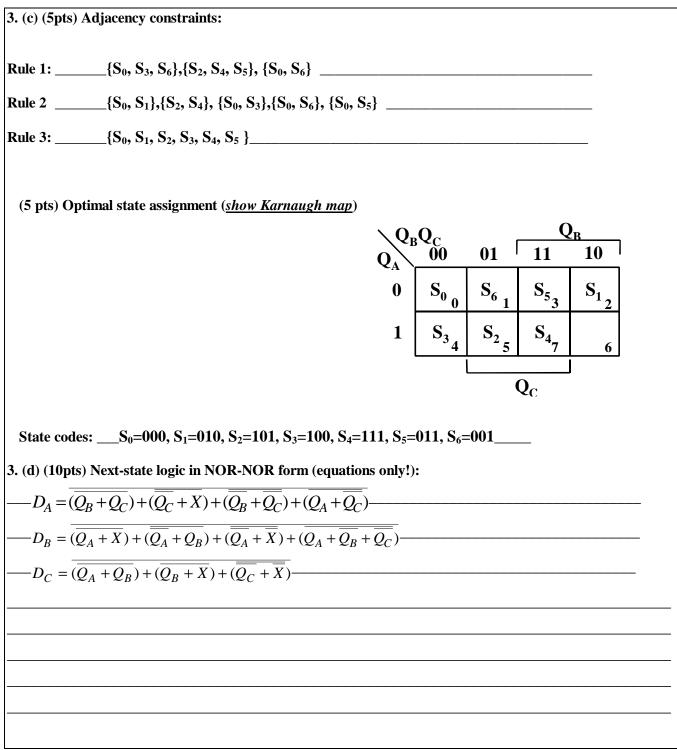

- (b) Use an **implication table** to determine if any states are equivalent. If so, **list the equivalent states** and then **re-draw your (now minimized) state diagram.**

- (c) Using **D** flip-flops and the state-assignment rules discussed in class, indicate all adjacency constraints for an optimal state encoding and determine an optimal encoding, listing the state codes for each state in the machine.

- (d) Write equations for the next-state logic only (not the output logic) using a minimal NOR-NOR two-level representation.

Additional space for Problem 3