#### **Outline**

#### O Last time:

- Combinational Testability and Test-pattern Generation

- → Faults in digital circuits

→ What is a test? : Controllability & Observability

- → Redundancy & testability

→ Test coverage & simple PODEM ATPG

→ Sequential Test: What are sequential faults?

- → SCAN Design

#### O This lecture:

- → Asynchronous Circuits

→ Moore and Mealy Standard Forms

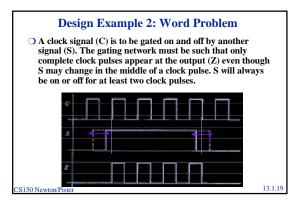

→ Design Example: Word Problem

S150 Newton/Pister

13.1.1

#### **Asynchronous Circuits** (Feedback Sequential Circuits)

#### O Clocked Synchronous Circuits:

- → Change of state only occurs in response to a clock pulse

- → When this change of state requires that a number of flip-flops change their values, they do so simultaneously because they are synchronized by the common clock pulse.

- Input changes are assumed to occur in between clock pulses and outputs may be read during or immediately before a clock pulse.

- O Conditions where this model is too restrictive:

- → The network has inputs which may change at any time and cannot be synchronized by a clock.

- → Signal travel time down wires is significant and wire lengths in the circuit cannot be controlled

→ We want the network to operate as fast as possible

- → The power dissipation overhead of clocking signals that do not change is unacceptable (we need "event-driven" circuits).

## **Asynchronous Circuits**

- Operation is not synchronized by a clock.

When an input change occurs, the state of the network can change almost immediately.

- → If several storage elements must change state, there is no guarantee they will do so at the same time.

- O To simplify this challenging problem we consider only fundamental

- The input signals will only change when the circuit is in a stable condition (i.e. no internal signals are changing).

- → All of the input signals are changing).

→ All of the input signals are considered to be levels, rather than pulses or edges.

→ Inputs may not change simultaneously

→ Asynchronous circuits may be structured as Mealy and Moore forms, as before, but delays in the feedback path are not clocked and may be different!

S150 Newton/Piste

# **D** Latch Example C-D+(C-D'+Y')' Q C·D'+Y' Excitation Equation for Y\*: $Y^* = CD + (CD' + Y')' = CD + C'Y + DY$

13.1.4

# **D** Latch Example: **Transition Table**

#### **D** Latch Example: **State Table**

= stable state

13.1

#### **Transition Table**

- A transition table has one row foreach possible combination of the state variables.

- → If the circuit has n feedback loops, it has 2^n rows in its transition table

- The table has one column for each input combination

- → A circuit with m inputs has 2<sup>m</sup> columns in its transition table.

- The circuit is monitoring its inputs continuously

CS150 Newton/Pister 13.1.7

#### **Total State**

- The total state of a circuit is a particular combination of the internal state (values stored in the feedback loops) and input state (the current values of the circuit inputs).

- A stable total state is a combination of internal state and input state such that the next internal state predicted by the transition table is the same as the current internal state.

- O If the next internal state is different, then the combination is an unstable total state

150 Newton/Pister 13.1.8

## **D Latch Example: Output Equations**

- Q = CD + C'Y + DY Q = CD' + Y'

- O Y is the only internal state variable

- O Combined state and output table:

|    |       | CD             |       |       |

|----|-------|----------------|-------|-------|

| S  | 00    | 01             | 11    | 10    |

| S0 | S0,01 | S0,01<br>S1,10 | S1,11 | S0,01 |

| S1 | S1,10 | S1,10          | S1,10 | S0,01 |

|    |       | S*, Q          | /Q    |       |

S150 Newton/Pister

#### **Races**

- O In a feedback sequential circuit, a race is said to occur when multiple internal variables change state as a result of a single input variable changing state.

- If the final state depends on the order in which the variables change, the race is said to be *critical*.

CS150 Newton/Pister 13.1.10

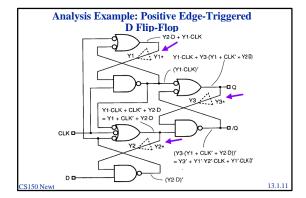

#### **Transition Table for D Flip-Flop** CLK D Y1Y2Y3 01 000 010 000 001 010 011 100 111 111 101 011 111 111 110 010 110 111 111 111 011 111 111 111 Y1\*Y2\*Y3\* 13 1 12

#### State and Output Table for D Flip-Flop

|              | CLK D        |              |              |        |  |  |  |  |  |  |

|--------------|--------------|--------------|--------------|--------|--|--|--|--|--|--|

| $\mathbf{S}$ | 00           | 01           | 11           | 10     |  |  |  |  |  |  |

| SO           | S2,01        | S2,01        | S0,01        | S0,01  |  |  |  |  |  |  |

| S1           | S3,10        | S3,10        | S0,01        | S0,01  |  |  |  |  |  |  |

| <b>S2</b>    | \$2,01       | S6,01        | S6,01        | S0,01  |  |  |  |  |  |  |

| S3           | <b>S3,10</b> | S7,10        | S7,10        | S0,01  |  |  |  |  |  |  |

| <b>S4</b>    | S2,01        | S2,01        | S7,11        | S7,11  |  |  |  |  |  |  |

| <b>S5</b>    | S3,10        | S3,10        | S7,10        | S7,10  |  |  |  |  |  |  |

| <b>S6</b>    | S2,01        | <b>S6,01</b> | S7,11        | S7,11  |  |  |  |  |  |  |

| <b>S7</b>    | S3,10        | \$7,10       | <b>§7,10</b> | \$7,10 |  |  |  |  |  |  |

|              | S*           |              |              |        |  |  |  |  |  |  |

13.1.13 S150 Newton/Pister

## Flow and Output Table for the D Flip-Flop

|           |        | (      | CLK D  |        |

|-----------|--------|--------|--------|--------|

| S         | 00     | 01     | 11     | 10     |

| S0        | S2,01  | S6,01  | \$0,01 | \$0,01 |

| S2        | S2,01  | S6,01  | -,-    | S0,01  |

| <b>S3</b> | \$3,10 | S7,10  | -,-    | S0,01  |

| <b>S6</b> |        | \$6,01 |        | -,-    |

| <b>S7</b> | S3 10  | \$7.10 | \$7,10 | 87.10  |

13.1.14 CS150 Newton/Piste

#### Steps to Asynchronous FSM Design

- O Construct a Primitive Flow Table from the word statement of the problem.

O Derive a minimum-row primitive flow table or *Reduced Primitive*

- Flow Table by eliminating redundant, stable total-states.

Convert the resulting table to Mealy form, if necessary, so that the output value is associated with the total state rather than the internal

- O Derive a minimum-row flow table, or Merged Flow Table, by merging compatible rows of the reduced primitive flow table using a merger diagram. (Note: solution not necessarily unique)

- Perform race-free, or critical-race-free, state assignment, adding additional states if necessary.

Complete the Output Table to avoid momentary false outputs when switching between stable total states.

- output functions as well as necessary delay elements.

S150 Newton/Pister

# **Design Example 1: Word Problem**

• An asynchronous network has two inputs and one output. The input sequence  $X_1X_2 = 00, 01, 11$  causes the output, Z, to become 1. The next input change then causes the output to return to 0. No other input sequence will produce a  $\boldsymbol{1}$ output.

Fundamental mode, single input changes, so input can only change in stable total state and only one bit can change, so this total-state is impossible, since only stable total state is inputs 00 in this part. this row.

#### **Derivation of Primitive Flow Table: Cont.**

| 2            | X1X          | 2   |     |    |   |

|--------------|--------------|-----|-----|----|---|

|              | 00           | 01  | 11  | 10 | Z |

| (reset) 1    | $\mathbb{C}$ | 2   | -   | 3  | 0 |

| (00,01) 2    | 1            | (2) | 4   | -  | 0 |

| (00,10) 3    | 1            | -   | 5   | 3  | 0 |

| (00,01,11) 4 |              |     | 4   | )  | 1 |

| (00,10,11) 5 |              |     | (5) | )  | 0 |

S150 Newton/Pister

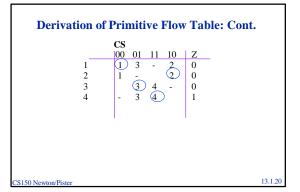

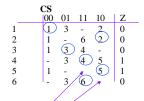

#### **Derivation of Primitive Flow Table: Cont.**

O Primitive Flow Table: Only one stable state per row is permitted, so every change in input must result in an internal state change as well as a toatl state change (by definition).

|                  | $\Delta 1 \Delta 1$ | _   |     |     |   |

|------------------|---------------------|-----|-----|-----|---|

|                  | 00                  | 01  | 11  | 10  | Z |

| (reset) 1        | 1                   | 2   | -   | 3   | 0 |

| (00,01) 2        | 1                   | (2) | 4   |     | 0 |

| (00,10) 3        | 1                   | -   | 5   | (3) | 0 |

| (00,01,11) 4     | -                   | 6   | 4   | 3   | 1 |

| * <del>,</del> 5 | -                   | 6   | (5) | 3   | 0 |

| * 6              | 1                   | 6   | 5   | -   | 0 |

States marked \* cannot lead to a 1 output without first resetting.

13 1 17

13 1 18

#### **Derivation of Primitive Flow Table: Cont.**

10->11 cannot occur in State 5 since S is assumed to be off for at least two clock pulses. Same for 11->10 in State 6.

13.1.21

S150 Newton/Pister

### **Steps to Asynchronous FSM Design**

- Construct a *Primitive Flow Table* from the word statement of the problem.

Derive a minimum-row primitive flow table or *Reduced Primitive Flow Table* by climinating redundant, stable total-states.

Convert the resulting table to Mealy form, if necessary, so that the output value is associated with the total state rather than the internal state.

Derive a minimum-row flow table, or *Merged Flow Table*, by merging compatible rows of the reduced primitive flow table using a merger diagram. (Note: solution not necessarily unique)

Perform race-free, or critical-race-free, state assignment, adding additional states if necessary.

Complete the *Output Table* to avoid momentary false outputs when switching between stable total states.

Draw *logic diagram* that shows ideal combinational next-state and output

- Draw logic diagram that shows ideal combinational next-state and output functions as well as necessary delay elements.

13.1.2 S150 Newton/Pister

#### **Minimum-Row Primitive Flow Table: Eliminate Redundant Stable Total States**

- O Redundant States: Two stable total states are equivalent if:

- (a) Their inputs are the same and

- (b) Their outputs are the same and

- (c) Their next-states are equivalent for each possible next input

In Example 1, possible candidates for combining are:

4.5] - no, because outputs not the same

{2,6} - no, because next-states not equivalent under 11 input (states 4 and 5)

so no redundant states here.

In Example 2, possible candidates are:

{4,6} - no, different outputs

{2,5} - no, different outputs

so no redundant states here either

13 1 2

# Removal of Redundant States: Example X1X2

|             | AIAZ                                   | •                             |      |      |         |                                                              |

|-------------|----------------------------------------|-------------------------------|------|------|---------|--------------------------------------------------------------|

|             | 00                                     | 01                            | 11   | 10   | Z1Z2    |                                                              |

| 1<br>2<br>3 | $\begin{vmatrix} 1 \\ 2 \end{vmatrix}$ | 7<br>5                        | -    | 4    | 1 1 0 1 | Examine stable states in same column (same input) that have  |

|             | -                                      | 7                             | 3    | 11   | 1 0     | same output:                                                 |

| 4           | 2                                      | Ō                             | 3    | (4)  | 0 0     | 00: {2,6,8} -under input 01, {2,6}<br>goe to different, not- |

| 5<br>6      | 16                                     | (2)                           | 9    | - 11 | 1 1     | equivalent next states.                                      |

| 7           | 6                                      | $\stackrel{\prime}{\bigcirc}$ | 14   | 11   | 0 1     | Similarly for {6,8}. {2,8} equiv. iff {5,12} equiv.          |

| 8           | 8                                      | 12                            | -    | 4    | 0 1     | 01: {5,12} - yes                                             |

| 9           | -                                      | 7                             | 9    | 13   | 0 1     | 11: {3,10} iff {4,11}                                        |

| 10          | -                                      | 7                             | (10) | 4    | 1 0     | 10: {4,11} iff {3,10} and {5,12}.                            |

| 11          | 8                                      | Ō                             | 10   | (11) | 0 0     | leads to:                                                    |

| 12          | 6                                      | (12)                          | 9    | Ō    | 1 1     |                                                              |

| 13          | 8                                      | -                             | 14   | (13) | 1 1     | {2,8}, {5,12}, {3,10}, {4,11}                                |

| 14          | 1 -                                    | 12                            | (14) | 11   | 0 0     | so eliminate 8, 10, 11, 12                                   |

| CLEO NI     |                                        |                               |      |      |         | 12                                                           |

13 1 2

| Remova              | xix2<br>00<br>-<br>2<br>6<br>6<br>1<br>-<br>2 | 01<br>7<br>5<br>7<br>5<br>7<br>7<br>7 | 11 - 3 3 9 - 14 9 14 14 | 10<br>4<br>4<br>4<br>4<br>-<br>4<br>-<br>13<br>13<br>4 | Z1Z2   1 1 | Exa | ample  |    |

|---------------------|-----------------------------------------------|---------------------------------------|-------------------------|--------------------------------------------------------|------------|-----|--------|----|

| CS150 Newton/Pister |                                               |                                       |                         |                                                        |            |     | 13.1.2 | 25 |