# Outline O Last time: → Deriving the State Diagram & Datapath (Cont.) → Mapping the Datapath onto Control O This lecture: Combinational Testability and Test-pattern Generation Faults in digital circuits What is a test?: Controllability & Observability Redundancy & testability Test coverage & simple PODEM ATPG Sequential Test: What are sequential faults? SCAN Design CS150 Newton/Pister 12.1.1

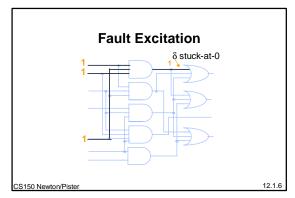

# **Fault Models**

- Input or output pin (not entire net!) stuck at logic 0 or stuck at logic 1.

- Open circuit

- Can make a combinational circuit sequential!

- Short circuit

12.1.7 S150 Newton/Pister

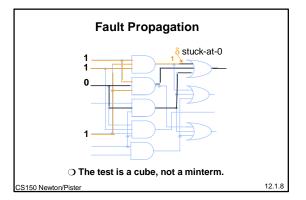

# Optimality & Redundancy in **Combinational Logic**

Circuit with redundant fault:

δ stuck-at-0 f = (a.b).(c+d).c' = (a.b.c + a.b.d).c' = a.b.c.c' + a.b.d.c' Circuit with  $\delta = 0$ f = (a.b).c'.d

= a.b.d.c'

S150 Newton/Pister

12.1.9

### Path-Oriented DEcision Making [Goel, 1981]

- (1) Assign all Primary Inputs (PI) to the value "don't care" ( ).

- (2) Given an output signal and a desired value for the output, trace a path to the PIs to obtain a PI assignment.

- (3) Simulate the PI vector to see if it sets up the desired value on the output. If so, terminate.

- (4) If the opposite value is set, assign an opposite value to the PI and re-simulate. If desired value is set, terminate.

- (5) If the output remains unspecified, repeat the path tracing to set another PI, as necessary.

- O Procedure continues until either:

- → A successful PI assignment has been found (circuits not equivalent).

- → All possible PI assignments have been exhausted.

12.1.10 CS150 Newton/Pister

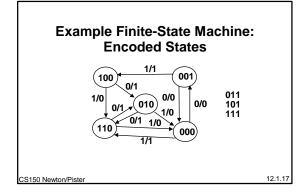

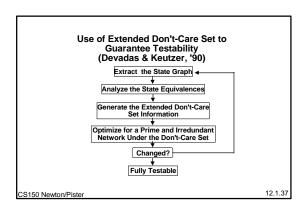

# **Cover Extraction** O Covers can be generated with as many "don't cares" in the present state part as possible. S150 Newton/Piste 12.1.1

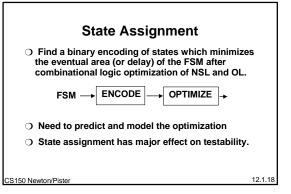

# **Testability and Logic Synthesis**

O Important Issue:

Generating tests for circuits with redundancies is very difficult.

→ Must use algorithms which decrease the number of redundancies or eliminate them completely during synthesis.

12 1 12

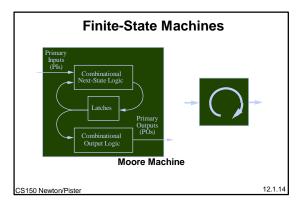

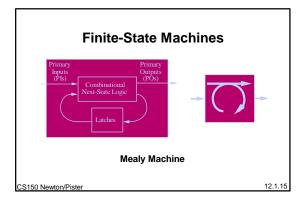

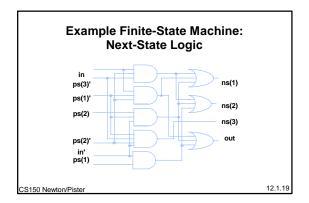

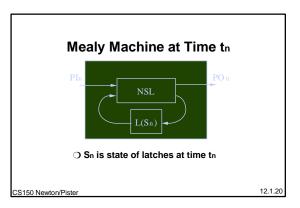

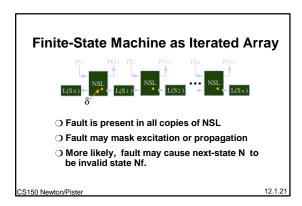

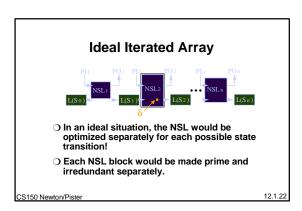

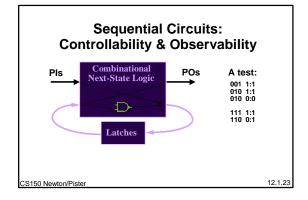

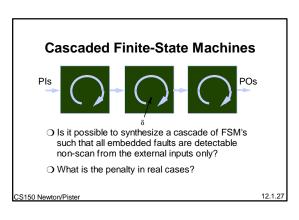

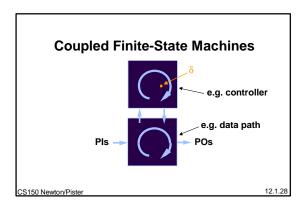

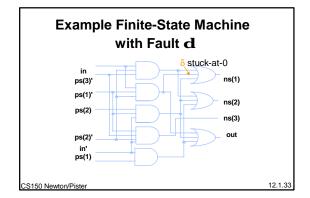

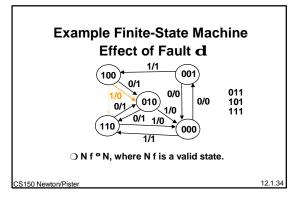

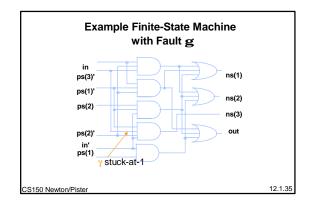

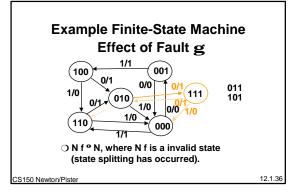

# Test Generation for Finite-State Machines

- Irredundant combinational logic does not imply 100% sequential testability

- Sequential Faults: Faults may not be excited ("controlled") by primary inputs; faults may not be propagated to primary outputs ("observed").

CS150 Newton/Pister 12.1.13

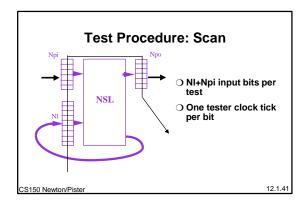

# Scan Design Make all flip-flops scan (i.e. direct read and write access) All inputs to the combinational logic can be set and all outputs can be read. The sequential testing problem becomes a combinational testing problem. "Overkill" in virtually all cases. Area and time penalty; often a longer testing time. But scan can be inserted automatically.

12.1.24

CS150 Newton/Pister

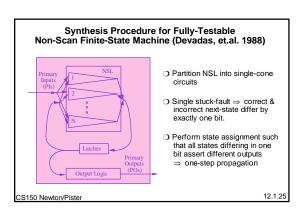

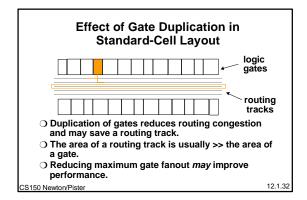

# Synthesis Procedure for Fully-Testable Non-Scan Finite-State Machines

Given a state-transition graph (STG) of a FSM, a 100%-testable logic-level implementation of the machine is produced

- O No scannable latches required

- O Uses partitioned logic approach and constrained state assignment

- Small penalty

CS150 Newton/Pister 12.1.26

| Example FSMs       |               |                |               |              |   |

|--------------------|---------------|----------------|---------------|--------------|---|

| Name               | No.<br>Inputs | No.<br>Outputs | No.<br>States | No.<br>Edges |   |

| sse                | 7             | 7              | 13            | 59           |   |

| tbk                | 6             | 3              | 16            | 787          |   |

| dfile              | 2             | 1              | 24            | 99           |   |

| planet             | 7             | 19             | 48            | 118          |   |

| scf                | 27            | 54             | 97            | 168          |   |

| S150 Newton/Pister |               |                |               |              | 1 |

| 1                                                                                    | Op           | timized onl        | v           | Optir        | nized and Te | estable     |

|--------------------------------------------------------------------------------------|--------------|--------------------|-------------|--------------|--------------|-------------|

| Name                                                                                 | No.<br>Gates | Fault<br>Cover (%) | TPG<br>time | No.<br>Gates | Fault        | TPG<br>time |

| sse                                                                                  | 91           | 84.6               | 70s         | 129          | 100          | 5s          |

| tbk                                                                                  | 181          | 98.6               | 72s         | 231          | 98.6         | 4s          |

| dfile                                                                                | 124          | 96.9               | 104s        | 144          | 100          | 2s          |

| planet                                                                               | 417          | 98.8               | 373s        | 449          | 100          | 14s         |

| scf 502 96.1 83m 541 100 71s Output logic block contained combinational redundancies |              |                    |             |              |              |             |

| Constrained State Assignment (single cones) |       |                                  |                           |                                      |         |

|---------------------------------------------|-------|----------------------------------|---------------------------|--------------------------------------|---------|

| Name                                        |       | mized only<br>Normalized<br>Area | Optimized<br>No.<br>Gates | d and Testable<br>Normalized<br>Area | €       |

| sse                                         | 91    | 1.00                             | 129                       | 1.34                                 |         |

| tbk                                         | 181   | 1.00                             | 231                       | 1.10                                 |         |

| dfile                                       | 124   | 1.00                             | 144                       | 0.98                                 |         |

| planet                                      | 417   | 1.00                             | 449                       | 0.86                                 |         |

| scf                                         | 502   | 1.00                             | 541                       | 1.01                                 |         |

| CS150 Newton/P                              | ister |                                  |                           | 1                                    | 12.1.31 |

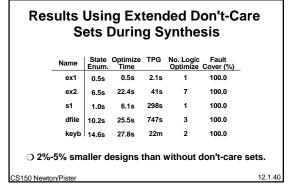

| Example FSMs        |               |                |               |              |         |

|---------------------|---------------|----------------|---------------|--------------|---------|

| Name                | No.<br>Inputs | No.<br>Outputs | No.<br>States | No.<br>Edges |         |

| ex1                 | 2             | 2              | 6             | 24           |         |

| ex2                 | 2             | 1              | 13            | 57           |         |

| s1                  | 8             | 6              | 20            | 110          |         |

| dfile               | 2             | 1              | 24            | 96           |         |

| keyb                | 7             | 2              | 19            | 170          |         |

| CS150 Newton/Pister |               |                |               |              | 12.1.38 |

### **Results of Synthesis Procedure** Fault Cover (%) 23 97.9 1.1s 2.0s ex1 35 2.2s 42s 6.1s 1.8m ex2 105 303s 4.0s s1 77 97.8 6.2s 332s >1h dfile 1.2m 12.1.39 CS150 Newton/Pister

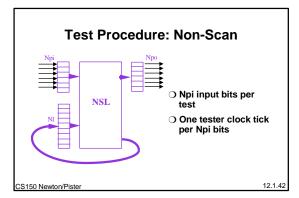

# What About Testing Time?

(Ghosh et. al. 1989)

| Nun<br>Name | nber of To<br>Scan | est Bits<br>S for T |

|-------------|--------------------|---------------------|

| ex1         | 4,032              | 13,728              |

| ex2         | 29,696             | 111,510             |

| ex3         | 55,680             | 134,290             |

| des         | 8768               | 22,826              |

| key         | 11,856             | 51,968              |

| viterbi     | 15,168             | 224,950             |

CS150 Newton/Pister 12.1.43

## Viterbi Chip

- Part of a system for real-time continuous speech recognition developed by Prof's. Broderson & Rabaey at Berkeley.

- O Largest chip in the chip-set for the system.

- Implements the Viterbi algorithm for mapping an observation (some speech) into the most likely sequence of states in the speech model being used.

- O Chip Statistics:

25,000 transistors 116 inputs, 44 outputs.

10 x11.5 mm die size

CS150 Newton/Pister 12.1.44

# What About Testing Time?

|         | Tester Cycles |         | Tes    | t Bits  |

|---------|---------------|---------|--------|---------|

| Name    | Scan          | S for T | Scan   | S for T |

| ex1     | 4,032         | 208     | 4,032  | 13,728  |

| ex2     | 29,696        | 590     | 29,696 | 111,510 |

| ex3     | 55,680        | 1,033   | 55,680 | 134,290 |

| des     | 8,768         | 202     | 8768   | 22,826  |

| key     | 11,856        | 203     | 11,856 | 51,968  |

| viterbi | 15,168        | 2,045   | 15,168 | 224,950 |

S150 Newton/Pister 12.1.45

### A Revolution in Test in the Late 1990s?

- Can Synthesize a Guaranteed Fully-Testable, Non-Scan Implementation of Any Collection of FSMs.

- √ Almost always requires fewer gates or less area than full scan.

- Almost always requires shorter tester times (in many cases by one or two orders of magnitude) than full scan.

- √ Can handle faults in embedded machines, machines with feedback, etc. - any topology of interconnected machines.

- √ Test patterns generated as a by-product of the synthesis, so synthesis time represents a saving of ATPG time.

CS150 Newton/Pister 12.1.46

# **Synthesis-Directed Sequential Test**

- Entire-chip full-scan-based design-for-test will be obsolete by the end of the 1990s

- → Will be used for some very-specific on-chip structures (e.g. ROM, RAM, maybe Datapath) and for some chip boundaries.

- Circuit-structure-specific and BILBO-like test styles will continue to be used for go-nogo tests.

- Architectural memory structures will continue to be accessible directly for the pins.

S150 Newton/Pister 12.1.47

# **Synthesis-Directed Sequential Test**

- Test will be incorporated directly into the synthesis process

- → Guaranteed fully-testable non-scan or partialscan designs will be produced by the synthesis process.

- → A complete set of test patterns will be a byproduct of the process

CS150 Newton/Pictor