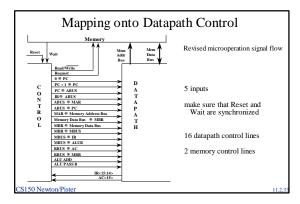

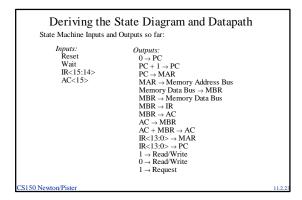

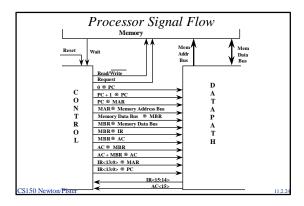

## Mapping onto Datapath Control Specification so far is independent of bussing strategy Implied transfers: This is the point-to-point connection scheme S150 Newton/Piste

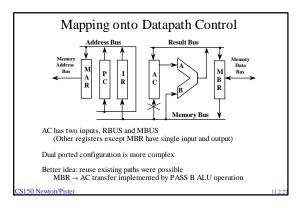

## Mapping onto Datapath Control

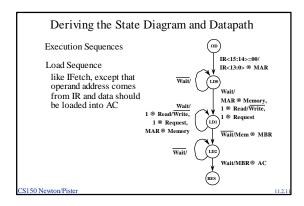

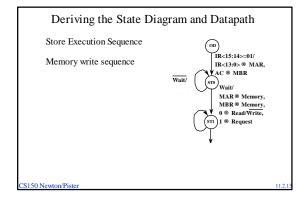

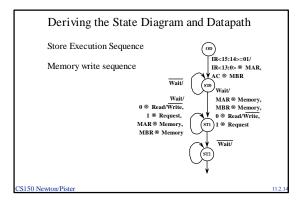

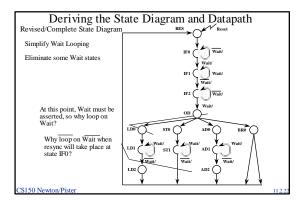

Observe that instruction fetch and operand fetch take place at

This implies that IR, PC, and MAR transfers can be implemented by single bus (Address Bus)

Combine MBR, IR, ALU B, and AC connections (Memory Bus)

Combine ALU, AC, and MBR connections (Result Bus)

Three bus architecture:  $AC + MBR \rightarrow AC \ implemented \ in \ single \ state$

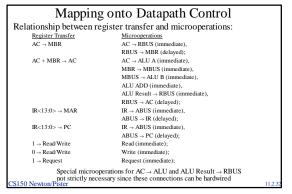

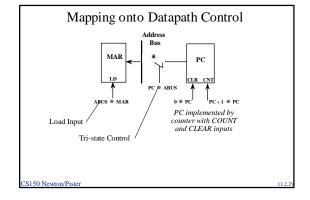

## Mapping onto Datapath Control

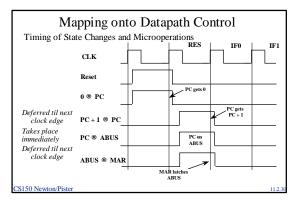

Detailed implementation of register transfer operations More detailed control operations are called microoperations

One register transfer operation = several microoperations

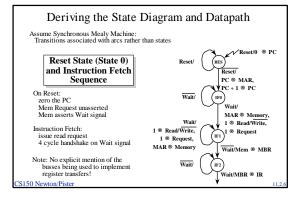

Some operations directly implemented by functional units: e.g., ADD, Pass B, 0 @ PC, PC + 1 @ PC

Some operations require multiple control operations: e.g., PC  $\rightarrow$  MAR implemented as PC  $\rightarrow$  ABUS and ABUS  $\rightarrow$  MAR

## Mapping onto Datapath Control Relationship between register transfer and microoperations: Register Transfer 0 PC Microoperations 0 ⊗ PC (delayed); PC + 1 ⊗ PC PC + 1 \* PC (delayed); PC \* MAR PC \* ABUS (immediate), ABUS \* MAR (delayed); MAR @ Address Bus MAR @ Address Bus (immediate): Data Bus \* MBR Data Bus \* MBR (delayed); MBR \* Data Bus MBR \* Data Bus (immediate); MBR \* IR MBR \* ABUS (immediate). ABUS \* IR (delayed): MBR \* AC MBR \* MBUS (immediate), MBUS \* ALU B (immediate), ALU PASS B (immediate), ALU Result \* RBUS (immediate), RBUS \* AC (delayed); S150 Newton/Pister