## **University of California at Berkeley College of Engineering Department of Electrical Engineering and Computer Sciences**

EECS150 J. Wawrzynek Spring 2000 E.Caspi

Quiz #12 - Solution

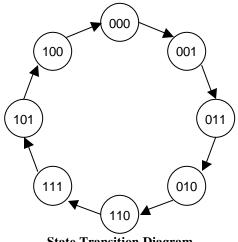

The counter FSM will represent the gray-code directly in 3 state bits. The next-state function will be the "next gray-code" function, and the counter output will be the state registers.

| State | <b>Transition</b> | Diagram |

|-------|-------------------|---------|

| - |       |       |       |            |        |        |

|---|-------|-------|-------|------------|--------|--------|

|   | State |       |       | Next State |        |        |

|   | $S_2$ | $S_1$ | $S_0$ | $NS_2$     | $NS_1$ | $NS_0$ |

|   | 0     | 0     | 0     | 0          | 0      | 1      |

|   | 0     | 0     | 1     | 0          | 1      | 1      |

|   | 0     | 1     | 0     | 1          | 1      | 0      |

|   | 0     | 1     | 1     | 0          | 1      | 0      |

|   | 1     | 0     | 0     | 0          | 0      | 0      |

|   | 1     | 0     | 1     | 1          | 0      | 0      |

|   | 1     | 1     | 0     | 1          | 1      | 1      |

|   | 1     | 1     | 1     | 1          | 0      | 1      |

**State Transition Table**

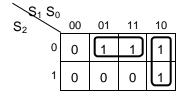

$$NS_0 = S'_2S'_1 + S_2S_1 = (S_2 \oplus S_1)'$$

$$NS_1 = S'_2S_0 + S_1S'_0$$

$$NS_2 = S_2S_0 + S_1S'_0$$

**Karnaugh Maps for Next State**

Reduced Logic Eqns