# Libraries Guide

Xilinx Unified Libraries

**Selection Guide**

Design Elements (ACC1 to BYPOSC)

**Design Elements (CAPTURE\_SPARTAN2** to DECODE64)

**Design Elements (F5MAP to FTSRLE)**

Design Elements (GCLK to KEEPER)

**Design Elements (LD to NOR16)**

Design Elements (OAND2 to OXOR2)

**Design Elements (PULLDOWN to ROM32X1)**

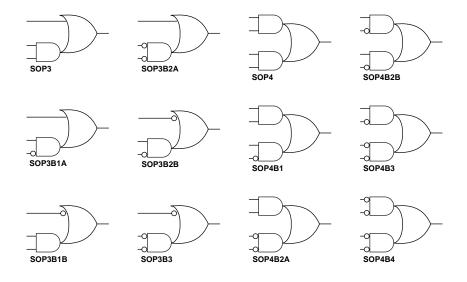

Design Elements (SOP3 to XORCY\_L)

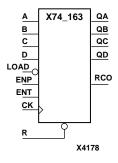

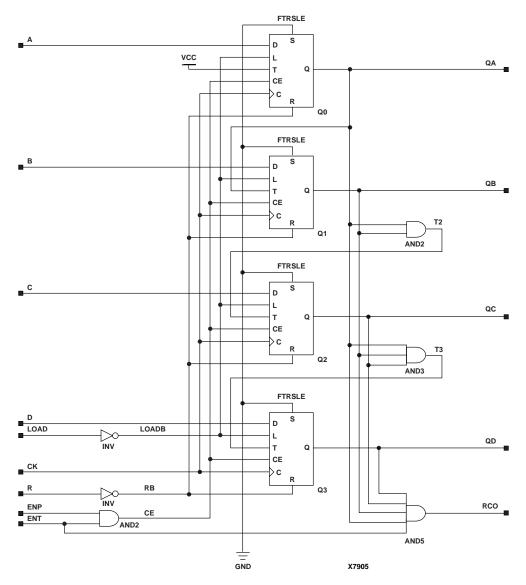

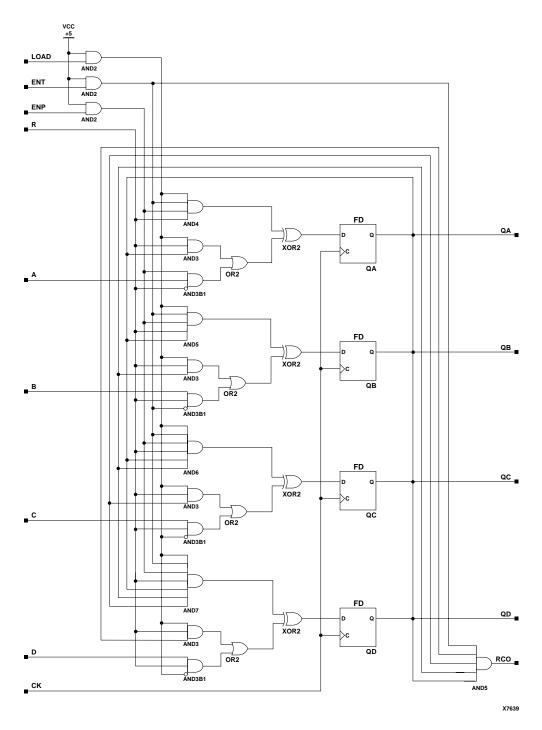

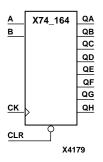

**Design Elements (X74\_42 to X74\_521)**

Attributes, Constraints, and Carry Logic

Libraries Guide, 2.1i Printed in U.S.A.

The Xilinx logo shown above is a registered trademark of Xilinx, Inc.

PGA Architect, FPGA Foundry, NeoCAD, NeoCAD EPIC, NeoCAD PRISM, NeoROUTE, Timing Wizard, TRACE, XACT, XILINX, XC2064, XC3090, XC4005, XC5210, and XC-DS501 are registered trademarks of Xilinx, Inc.

The shadow X shown above is a trademark of Xilinx, Inc.

All XC-prefix product designations, A.K.A. Speed, Alliance Series, AllianceCORE, BITA, CLC, Configurable Logic Cell, CORE Generator, CoreGenerator, CoreLINX, Dual Block, EZTag, FastCLK, FastCONNECT, FastFLASH, FastMap, Foundation, HardWire, LCA, LogiBLOX, Logic Cell, LogicORE, LogicProfessor, MicroVia, PLUSASM, PowerGuide, PowerMaze, QPro, RealPCI, RealPCI 64/66, SelectI/O, Select-RAM, Select-RAM+, Smartguide, Smart-IP, SmartSearch, Smartspec, SMARTSwitch, Spartan, TrueMap, UlM, VectorMaze, VersaBlock, VersaRing, Virtex, WebLINX, XABEL, XACTstep, XACTstep Advanced, XACTstep Foundry, XACT-Floorplanner, XACT-Performance, XAM, XAPP, X-BLOX, X-BLOX plus, XChecker, XDM, XDS, XEPLD, Xilinx Foundation Series, XPP, XSI, and ZERO+ are trademarks of Xilinx, Inc. The Programmable Logic Company and The Programmable Gate Array Company are service marks of Xilinx, Inc.

All other trademarks are the property of their respective owners.

Xilinx, Inc. does not assume any liability arising out of the application or use of any product described or shown herein; nor does it convey any license under its patents, copyrights, or maskwork rights or any rights of others. Xilinx, Inc. reserves the right to make changes, at any time, in order to improve reliability, function or design and to supply the best product possible. Xilinx, Inc. will not assume responsibility for the use of any circuitry described herein other than circuitry entirely embodied in its products. Xilinx, Inc. devices and products are protected under one or more of the following U.S. Patents: 4,642,487; 4,695,740; 4,706,216; 4,713,557; 4,746,822; 4,750,155; 4,758,985; 4,820,937; 4,821,233; 4,835,418;  $4,855,619; \ 4,855,669; \ 4,902,910; \ 4,940,909; \ 4,967,107; \ 5,012,135; \ 5,023,606; \ 5,028,821; \ 5,047,710; \ 5,068,603; \ 5,140,193; \ 5,148,390; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,140,193; \ 5,1$ 5,155,432; 5,166,858; 5,224,056; 5,243,238; 5,245,277; 5,267,187; 5,291,079; 5,295,090; 5,302,866; 5,319,252; 5,319,254; 5,321,704; 5,329,174; 5,329,181; 5,331,220; 5,331,226; 5,332,929; 5,337,255; 5,343,406; 5,349,248; 5,349,249; 5,349,250; 5,349,691; 5,357,153; 5,360,747; 5,361,229; 5,362,999; 5,365,125; 5,367,207; 5,386,154; 5,394,104; 5,399,924; 5,399,925; 5,410,189; 5,410,194; 5,414,377; 5,422,833; 5,426,378; 5,426,379; 5,430,687; 5,432,719; 5,448,181; 5,448,493; 5,450,021; 5,450,022; 5,453,706; 5,455,525; 5,466,117; 5,469,003; 5,475,253; 5,477,414; 5,481,206; 5,483,478; 5,486,707; 5,486,776; 5,488,316; 5,489,858; 5,489,866; 5,491,353; 5,495,196; 5,498,979; 5,498,989; 5,499,192; 5,500,608; 5,500,609; 5,502,000; 5,502,440; 5,504,439; 5,506,518; 5,506,523; 5,506,878; 5,513,124; 5,517,135; 5,521,835; 5,521,837; 5,523,963; 5,523,971; 5,524,097; 5,526,322; 5,528,169; 5,528,176; 5,530,378; 5,530,384; 5,546,018; 5,550,839; 5,550,843; 5,552,722; 5,553,001; 5,559,751; 5,561,367; 5,561,629; 5,561,631; 5,563,527; 5,563,528; 5,563,529; 5,563,529; 5,563,827; 5,565,792; 5,566,123; 5,570,051; 5,574,634; 5,574,655; 5,578,946; 5,581,198; 5,581,199; 5,581,738; 5,583,450; 5,583,452; 5,592,105; 5,594,367; 5,598,424; 5,600,263; 5,600,264; 5,600,271; 5,600,597; 5,608,342; 5,610,536; 5,610,790; 5,610,829; 5,612,633; 5,617,021; 5,617,041; 5,617,327; 5,617,573; 5,623,387; 5,627,480; 5,629,637; 5,629,886; 5,631,577; 5,631,583; 5,635,851; 5,636,368; 5,640,106; 5,642,058; 5,646,545; 5,646,547; 5,646,564; 5,646,903; 5,648,732; 5,648,913; 5,650,672; 5,650,946; 5,652,904; 5,654,631; 5,656,950; 5,657,290; 5,659,484; 5,661,660; 5,661,685; 5,670,896; 5,670,897; 5,672,966; 5,673,198; 5,675,262; 5,675,270; 5,675,589; 5,677,638; 5,682,107; 5,689,133; 5,689,516; 5,691,907; 5,691,912; 5,694,047; 5,694,056; 5,724,276; 5,694,399; 5,696,454; 5,701,091; 5,701,441; 5,703,759; 5,705,932; 5,705,938; 5,708,597; 5,712,579; 5,715,197; 5,717,340; 5,719,506; 5,719,507; 5,724,276; 5,726,484; 5,726,584; 5,734,866; 5,734,868; 5,737,234; 5,737,235; 5,737,631; 5,742,178; 5,742,531; 5,744,974; 5,744,979; 5,744,995; 5,748,942; 5,748,979; 5,752,006; 5,752,035; 5,754,459; 5,758,192; 5,760,603; 5,760,604; 5,760,607; 5,761,483; 5,764,076; 5,764,534; 5,764,564; 5,768,179; 5,770,951; 5,773,993; 5,778,439; 5,781,756; 5,784,313; 5,784,577; 5,786,240; 5,787,007; 5,789,938; 5,790,479; 5,790,882; 5,795,068; 5,796,269; 5,798,656; 5,801,546; 5,801,547; 5,801,548; 5,811,985; 5,815,004; 5,815,016; 5,815,404; 5,815,405; 5,818,255; 5,821,772; 5,821,774; 5,825,202; 5,825,662; 5,825,787; 5,828,230; 5,828,231; 5,828,236; 5,828,608; 5,831,448; 5,831,460; 5,831,845; 5,831,907; 5,835,402; 5,838,167; 5,838,901; 5,838,954; 5,841,296; 5,841,867; 5,844,422; 5,844,424; 5,844,829; 5,844,844; 5,847,577; 5,847,579; 5,847,580; 5,847,993; 5,852,323; Re. 34,363, Re. 34,444, and Re. 34,808. Other U.S. and foreign patents pending. Xilinx, Inc. does not represent that devices shown or products described herein are free from patent infringement or from any other third party light. Xilinx, Inc. assumes no obligation to correct any errors contained herein or to advise any user of this text of any correction if such be made. Xilinx, Inc. will not assume any liability for the accuracy or correctness of any engineering or software support or assistance provided to a user.

Xilinx products are not intended for use in life support appliances, devices, or systems. Use of a Xilinx product in such applications without the written consent of the appropriate Xilinx officer is prohibited.

Copyright 1991-1999 Xilinx, Inc. All Rights Reserved.

#### **About This Manual**

This manual describes Xilinx's Unified Libraries and the attributes and constraints that can be used with the components.

Before using this manual, you should be familiar with the operations that are common to all Xilinx software tools: how to bring up the system, select a tool for use, specify operations, and manage design data. These topics are covered in the *Quick Start Guide*.

#### **Additional Resources**

For additional information, go to http://support.xilinx.com. The following table lists some of the resources you can access from this page. You can also directly access some of these resources using the provided URLs.

| Resource          | Description/URL                                                                                                                                                                                                                                         |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tutorial          | Tutorials covering Xilinx design flows, from design entry to verification and debugging http://support.xilinx.com/support/techsup/tutorials/index.htm                                                                                                   |

| Answers Database  | Current listing of solution records for the Xilinx software tools Search this database using the search function at http://support.xilinx.com/support/searchtd.htm                                                                                      |

| Application Notes | Descriptions of device-specific design techniques and approaches<br>http://support.xilinx.com/apps/appsweb.htm                                                                                                                                          |

| Data Book         | Pages from The Programmable Logic Data Book, which describe device-specific information on Xilinx device characteristics, including readback, boundary scan, configuration, length count, and debugging http://support.xilinx.com/partinfo/databook.htm |

| Xcell Journals    | Quarterly journals for Xilinx programmable logic users http://support.xilinx.com/xcell/xcell.htm                                                                                                                                                        |

| Tech Tips         | Latest news, design tips, and patch information on the Xilinx design environment http://support.xilinx.com/support/techsup/journals/index.htm                                                                                                           |

# **Manual Contents**

This manual contains the following chapters.

- Chapter 1, "Xilinx Unified Libraries"

- Chapter 2, "Selection Guide"

- Chapter 3, "Design Elements (ACC1 to BYPOSC)"

- Chapter 4, "Design Elements (CAPTURE\_SPARTAN2 to DECODE64)"

Libraries Guide, 2.1i i

- Chapter 5, "Design Elements (F5MAP to FTSRLE)"

- Chapter 6, "Design Elements (GCLK to KEEPER)"

- Chapter 7, "Design Elements (LD to NOR16)"

- Chapter 8, "Design Elements (OAND2 to OXOR2)"

- Chapter 9, "Design Elements (PULLDOWN to ROM32X1)"

- Chapter 10, "Design Elements (SOP3 to XORCY\_L)"

- Chapter 11, "Design Elements (X74\_42 to X74\_521)"

- Chapter 12, "Attributes, Constraints, and Carry Logic"

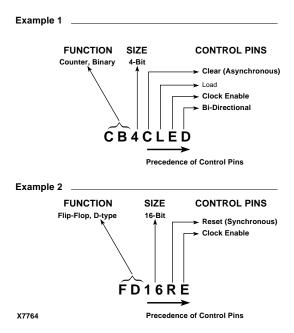

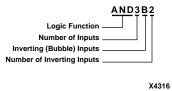

Chapter 1, "Xilinx Unified Libraries," discusses the unified libraries, applicable device architectures for each library, contents of the other chapters, general naming conventions, and performance issues.

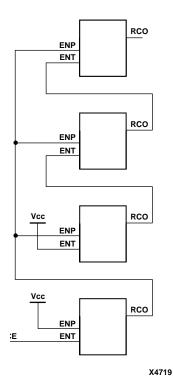

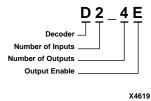

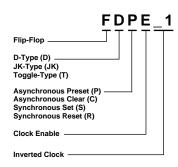

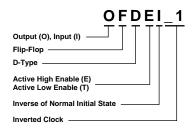

Chapter 2, "Selection Guide," describes then lists design elements by function that are explained in detail in the "Design Elements" chapters.

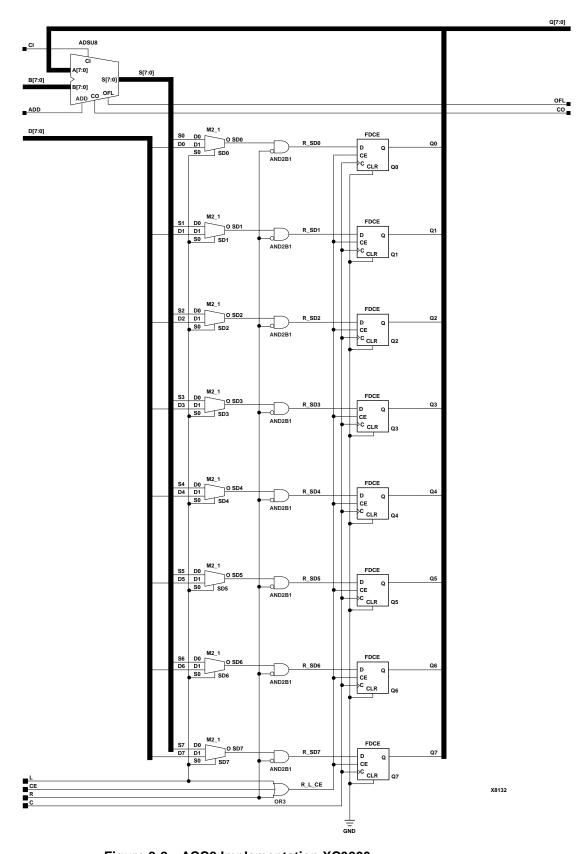

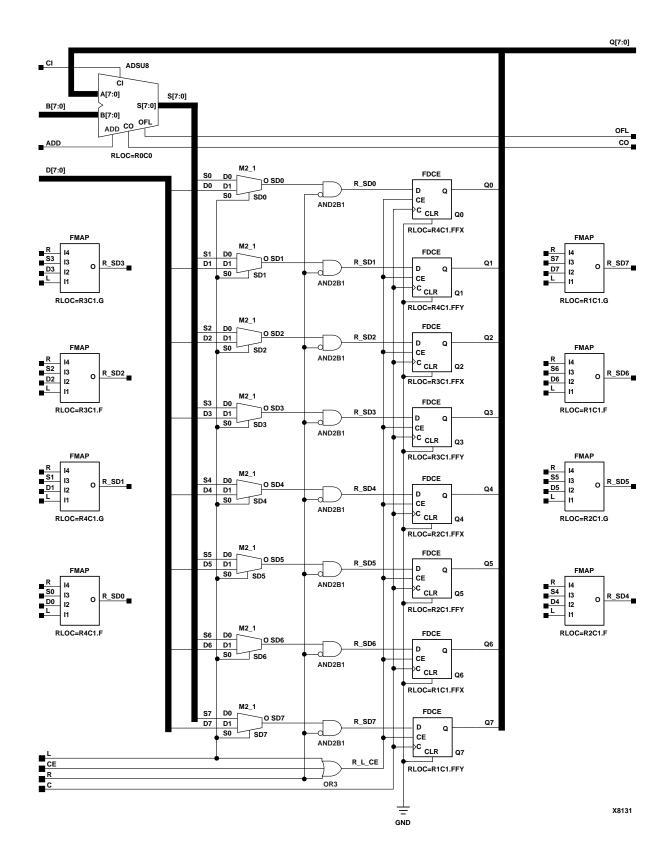

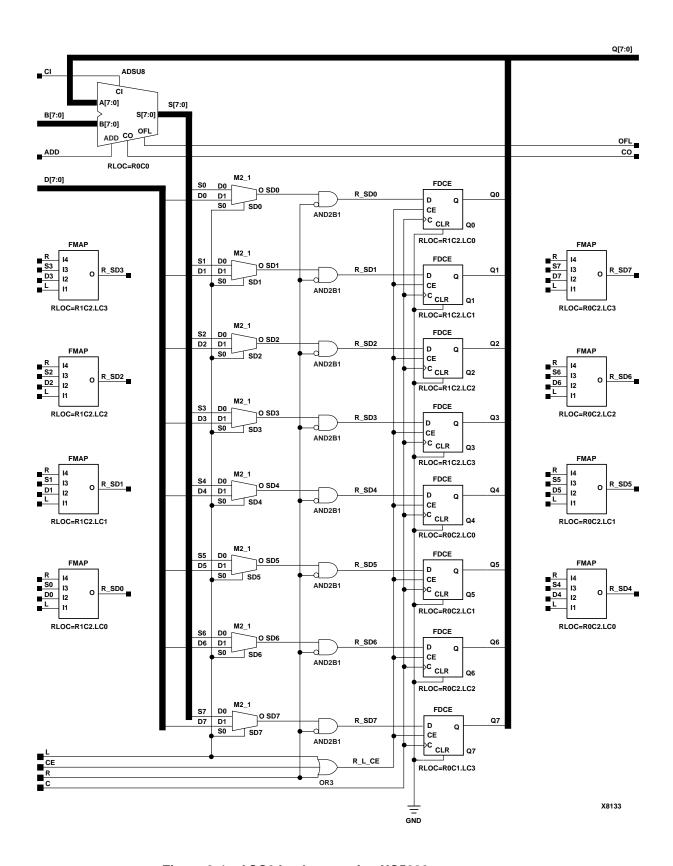

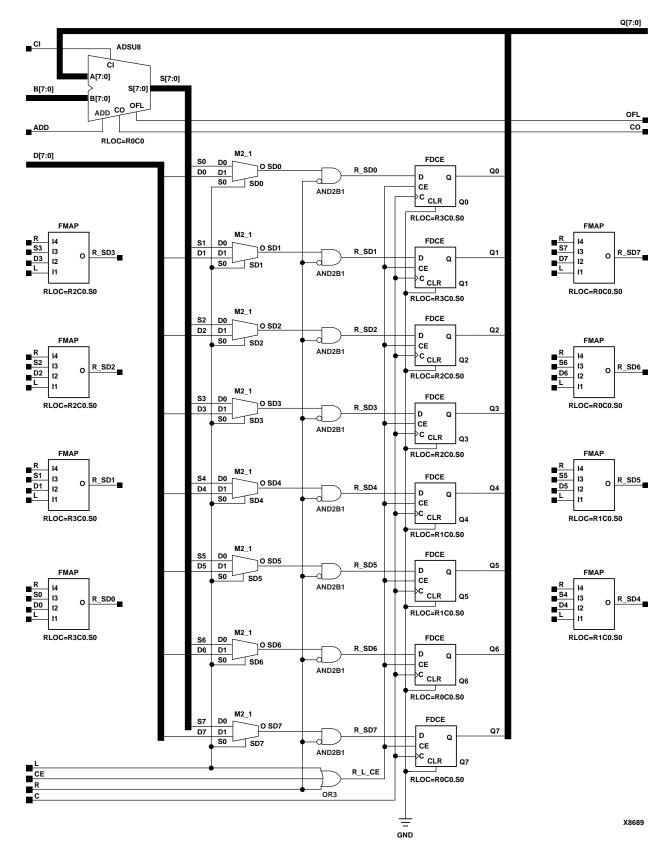

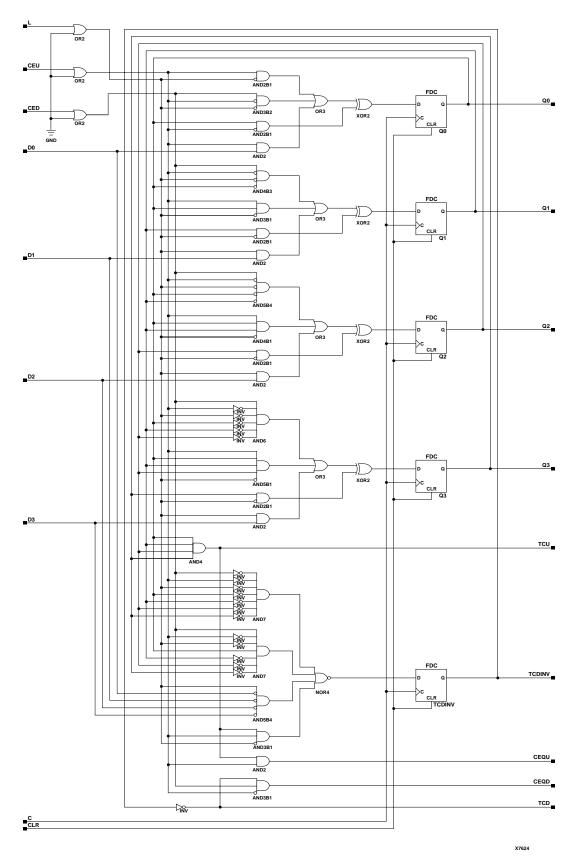

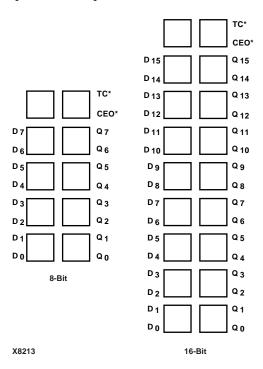

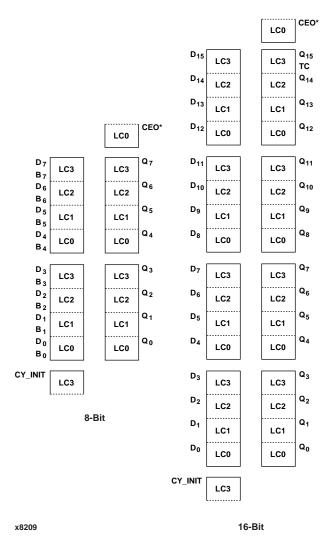

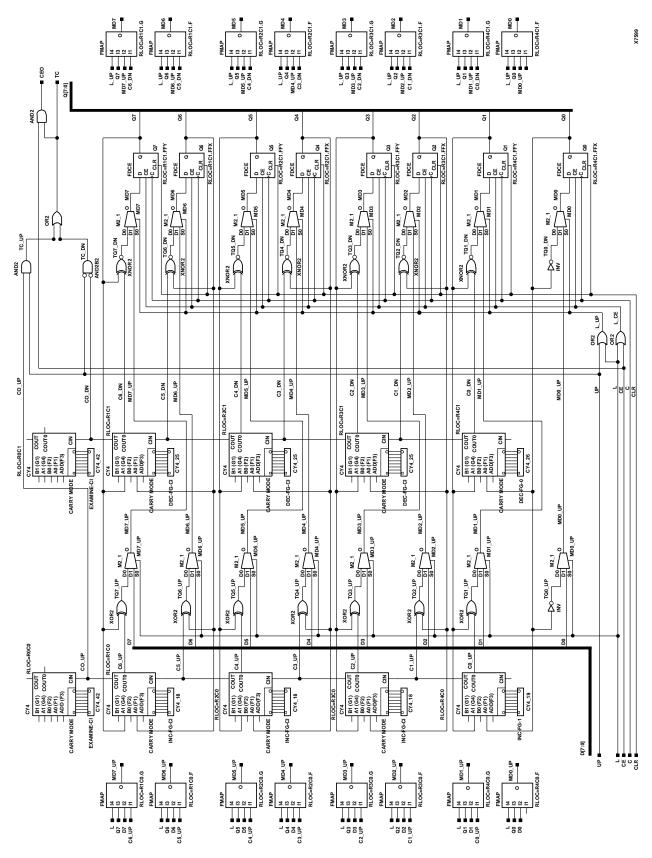

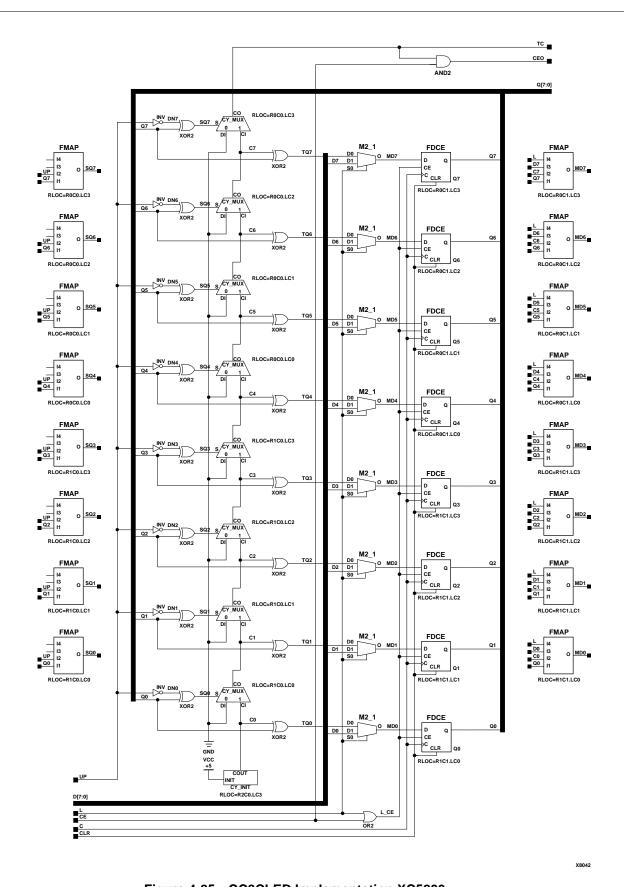

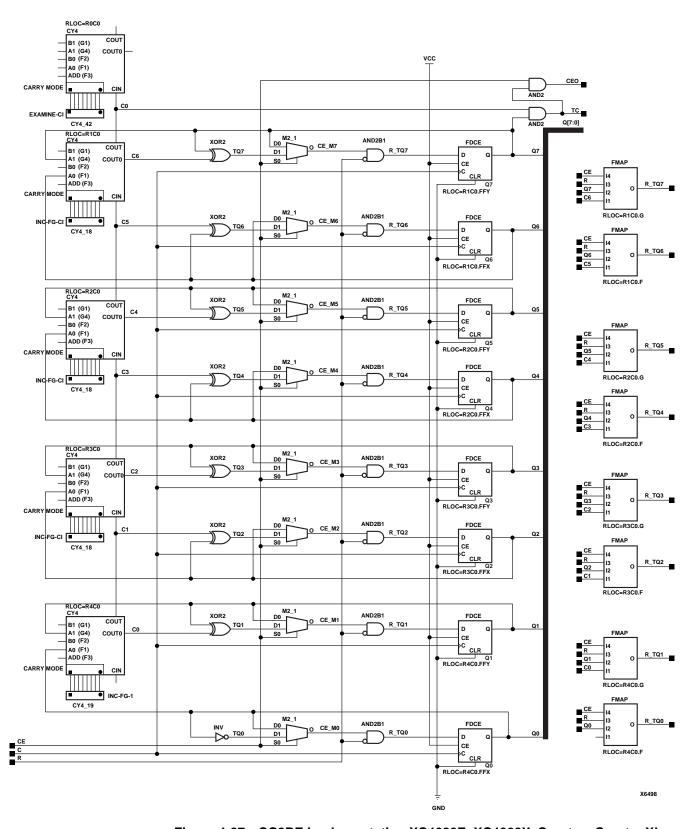

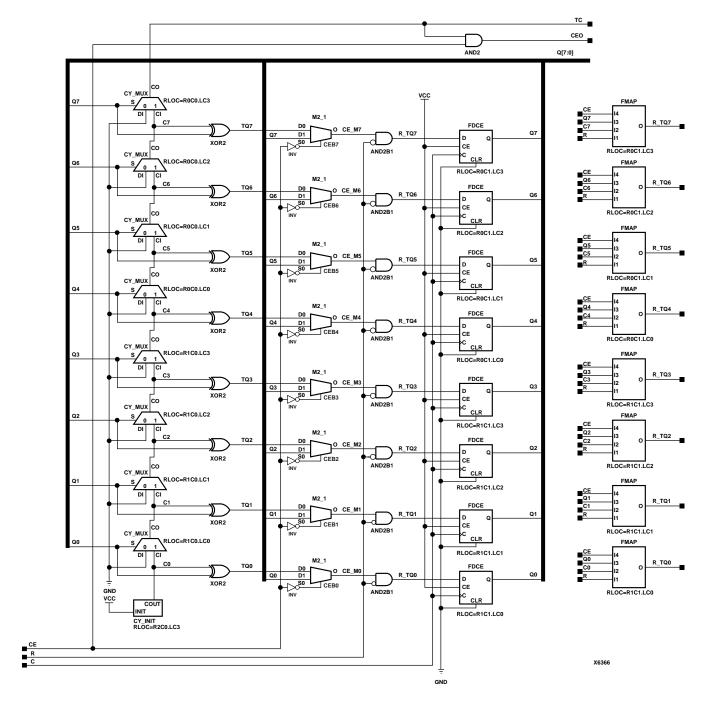

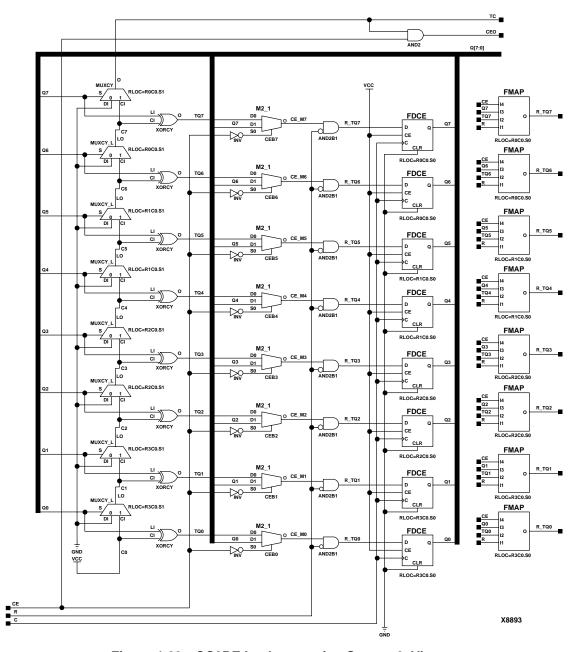

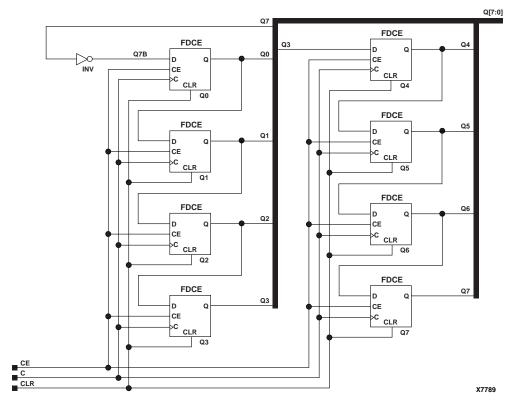

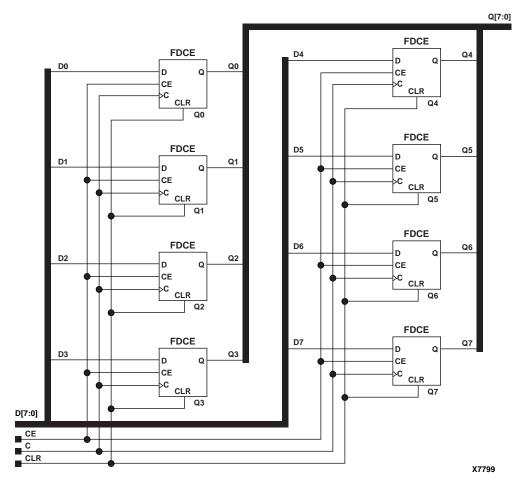

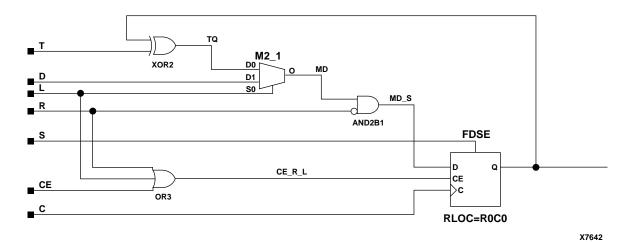

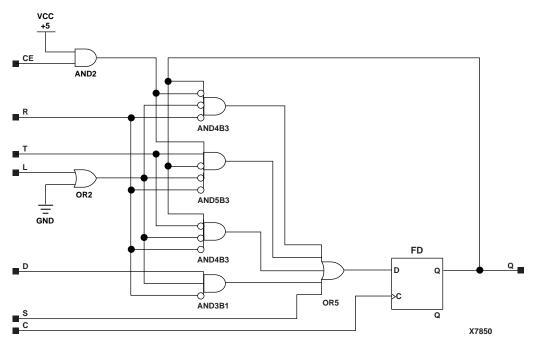

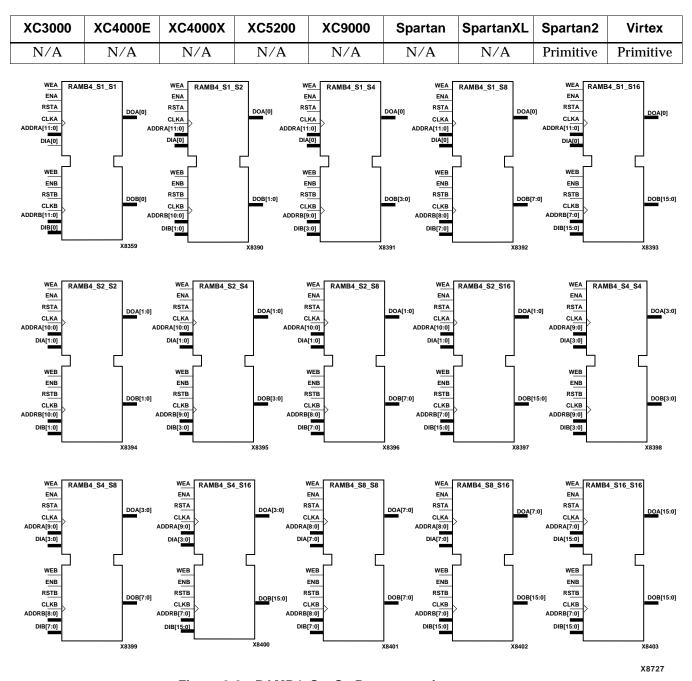

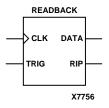

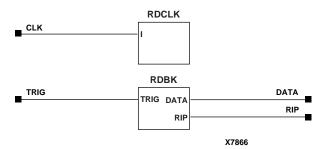

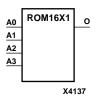

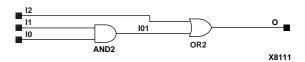

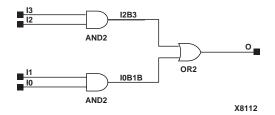

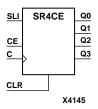

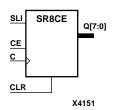

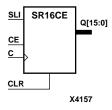

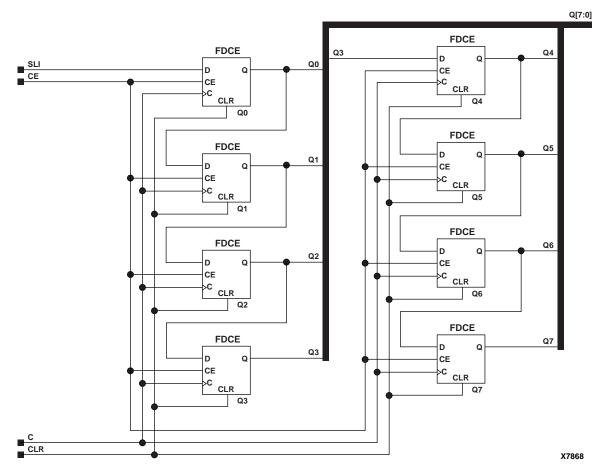

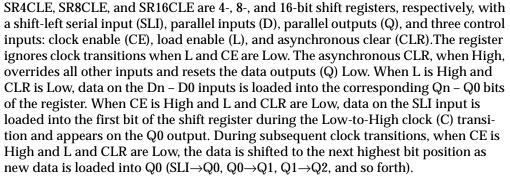

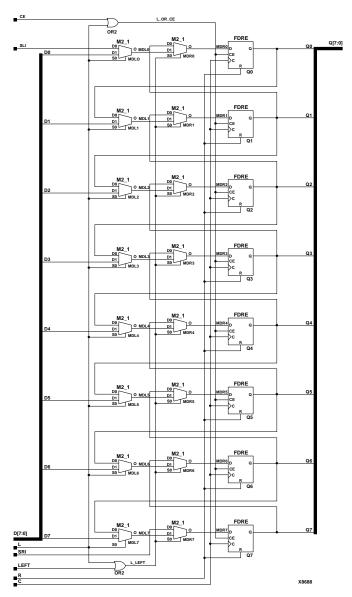

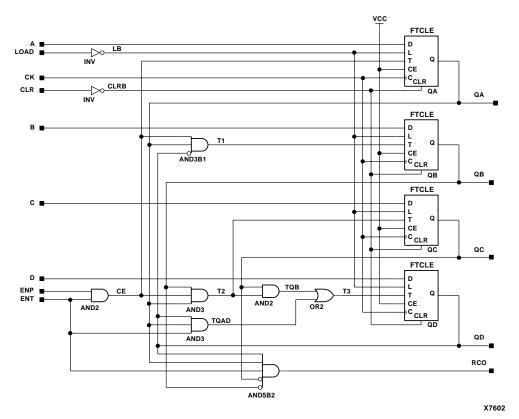

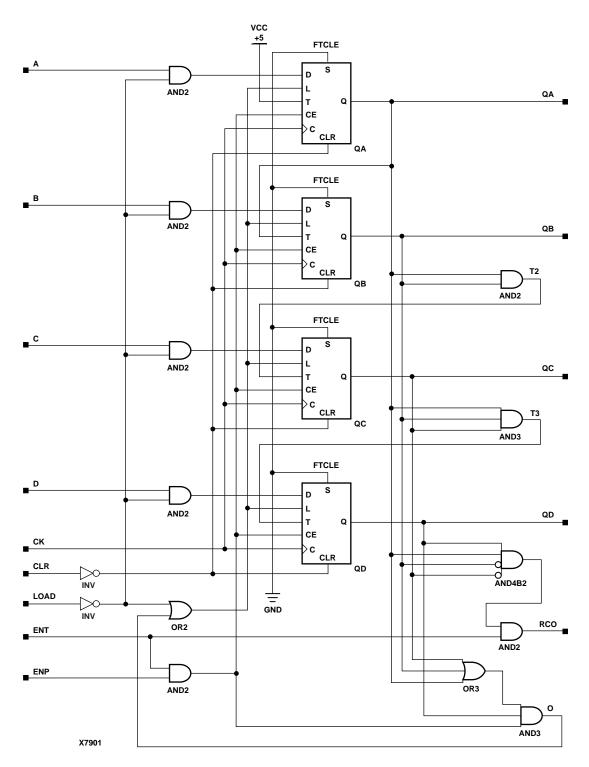

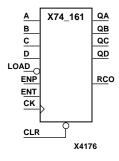

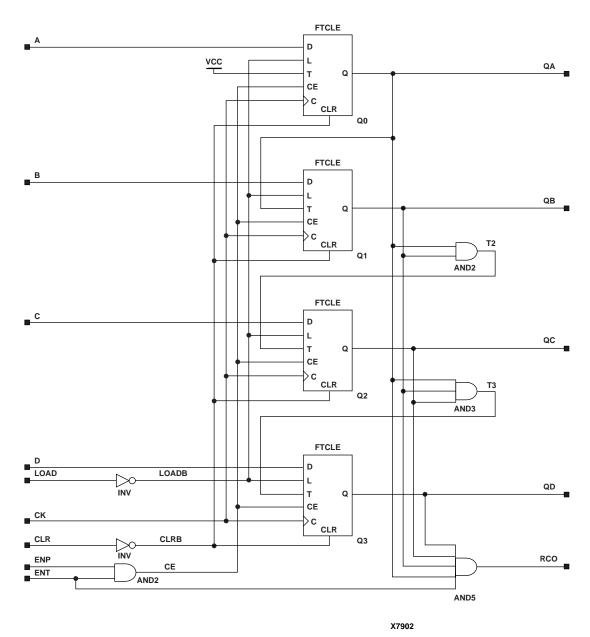

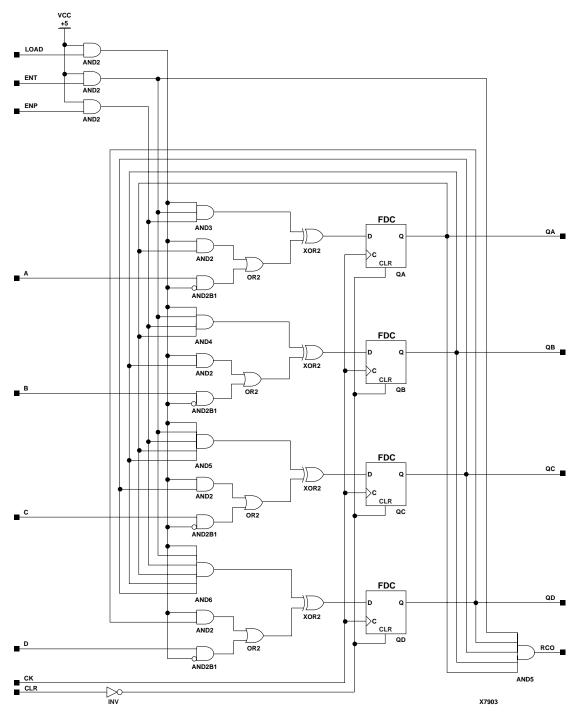

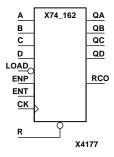

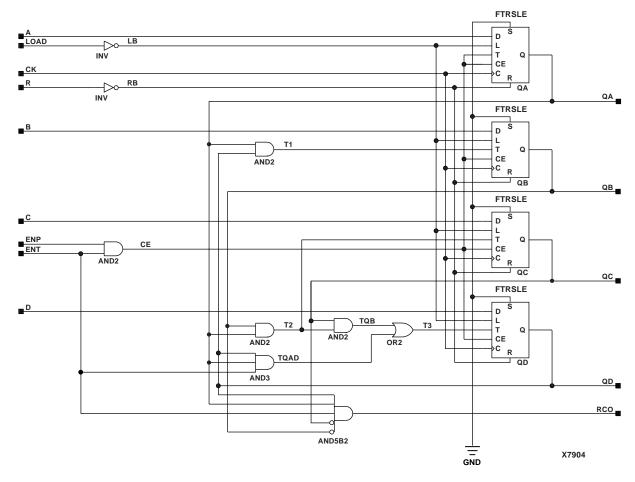

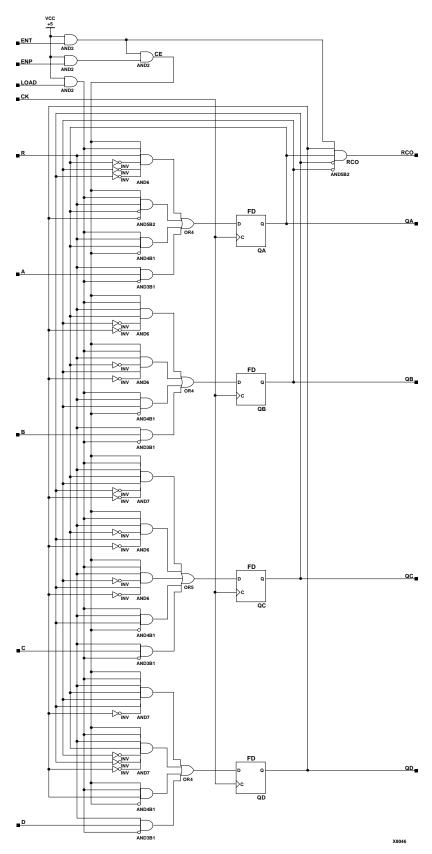

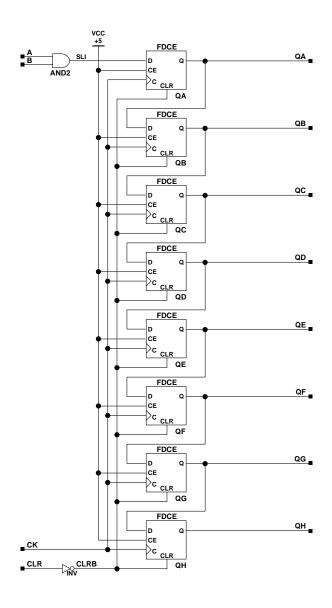

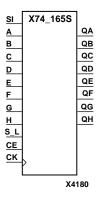

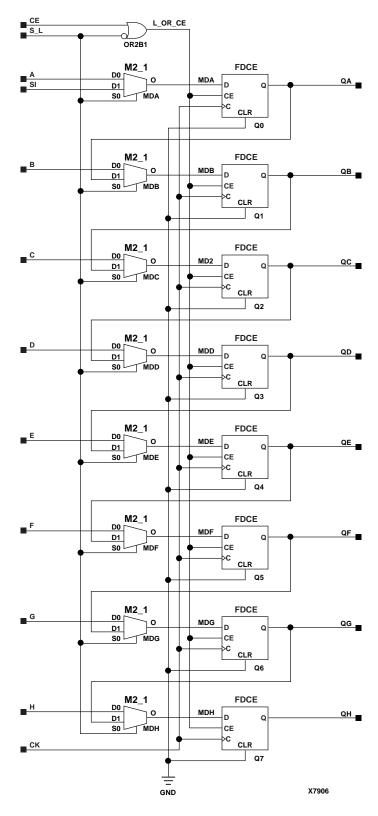

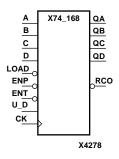

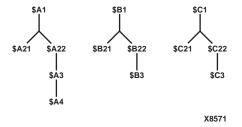

Chapters 3 through 11, "Design Elements," provide a graphic symbol, functional description, primitive versus macro table, truth table (when applicable), topology (when applicable), and schematics for macros of the design elements.

Chapter 12, "Attributes, Constraints, and Carry Logic," provides information on all attributes, logical constraints, placement and timing constraints, relationally placed macros (RPMs), and carry logic.

# **Contents**

| Manual                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| Additional Resources  Manual Contents                                                                                                                                                                                                                                                                                                                                      |                                                                                                       |

| s                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                       |

| TypographicalOnline Document                                                                                                                                                                                                                                                                                                                                               |                                                                                                       |

| Xilinx Unified Libraries                                                                                                                                                                                                                                                                                                                                                   |                                                                                                       |

| Overview Applicable Architectures XC3000 Library XC4000E Library XC4000X Library XC4000 XC5200 Library XC9000 Library Spartan Library Spartan Library Spartan Library Spartans Virtex Library Selection Guide Design Elements Schematic Examples Naming Conventions Attributes, Constraints, and Carry Logic Flip-Flop, Counter, and Register Performance Unconnected Pins | 1-2<br>1-2<br>1-2<br>1-3<br>1-3<br>1-3<br>1-3<br>1-3<br>1-3<br>1-4<br>1-4<br>1-4<br>1-5<br>1-5<br>1-6 |

| Selection Guide                                                                                                                                                                                                                                                                                                                                                            |                                                                                                       |

| CLB Count Relationally Placed Macros. Functional Categories Arithmetic Functions Buffers Comparators Counters Data Registers Decoders Edge Decoders                                                                                                                                                                                                                        | 2-10<br>2-12<br>2-13<br>2-14<br>2-16<br>2-17<br>2-21<br>2-22                                          |

|                                                                                                                                                                                                                                                                                                                                                                            | Additional Resources Manual Contents                                                                  |

Libraries Guide, 2.1i iii

|           | Flip-Flops                                                                          | . 2–24 |

|-----------|-------------------------------------------------------------------------------------|--------|

|           | General                                                                             |        |

|           | Input/Output Flip-Flops                                                             |        |

|           | Input/Output Functions                                                              |        |

|           | Input Latches                                                                       |        |

|           | Latches                                                                             |        |

|           | Logic Primitives                                                                    |        |

|           | Map Elements                                                                        |        |

|           | Memory Elements                                                                     |        |

|           |                                                                                     |        |

|           | Multiplexers                                                                        |        |

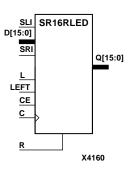

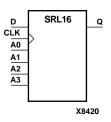

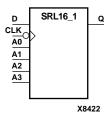

|           | Shift Registers                                                                     |        |

|           | Shifters                                                                            | . 2–57 |

| Chapter 3 | Design Elements (ACC1 to BYPOSC)                                                    |        |

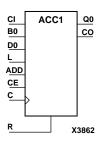

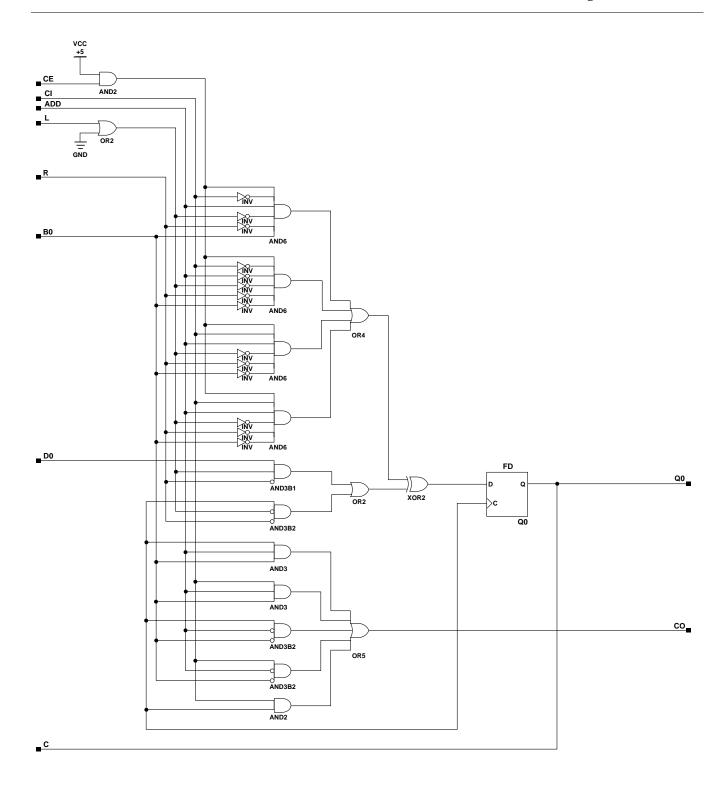

|           | ACC1                                                                                | . 3-2  |

|           | 1-Bit Loadable Cascadable Accumulator with Carry-In, Carry-Out, and Synchronous     |        |

|           | Reset                                                                               | . 3-2  |

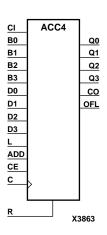

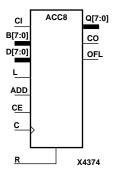

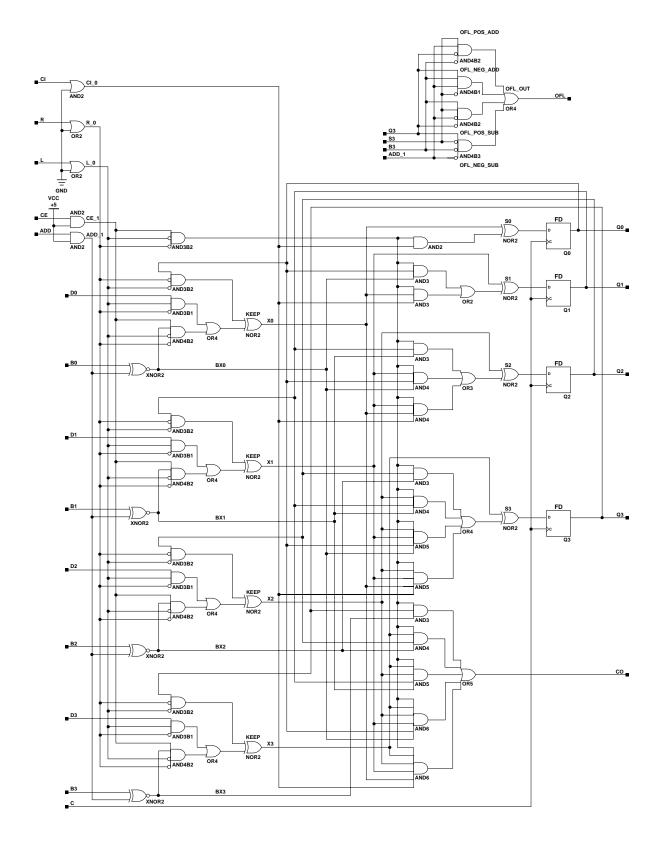

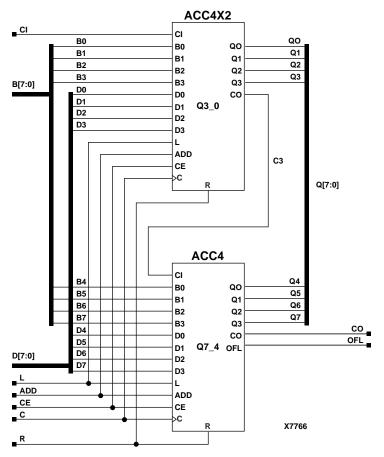

|           | ACC4, 8, 16                                                                         | . 3-4  |

|           | 4-, 8-, 16-Bit Loadable Cascadable Accumulators with Carry-In, Carry-Out, and       |        |

|           | Synchronous Reset                                                                   | . 3-4  |

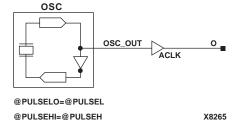

|           | ACLK                                                                                |        |

|           | Alternate Clock Buffer                                                              |        |

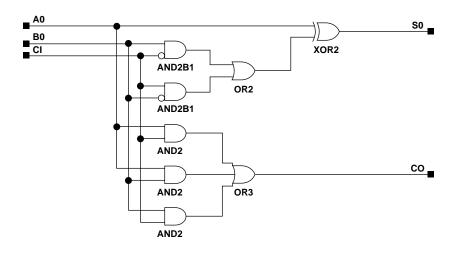

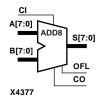

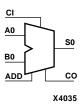

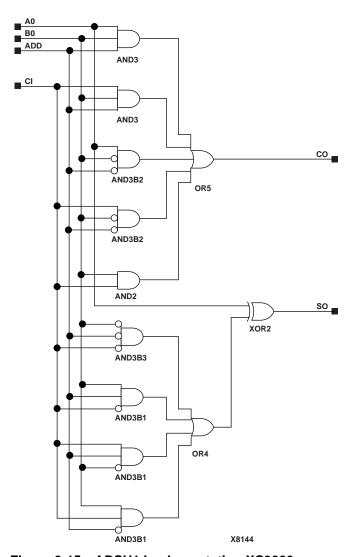

|           | ADD1                                                                                |        |

|           | 1-Bit Full Adder with Carry-In and Carry-Out                                        |        |

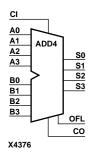

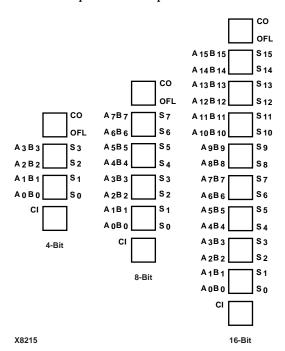

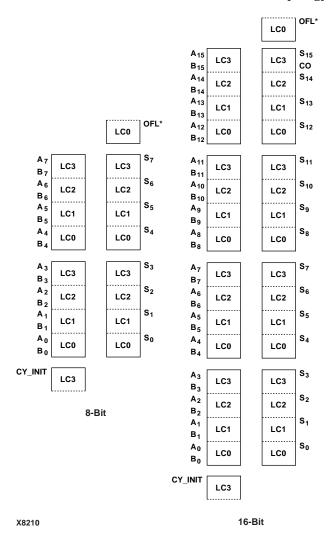

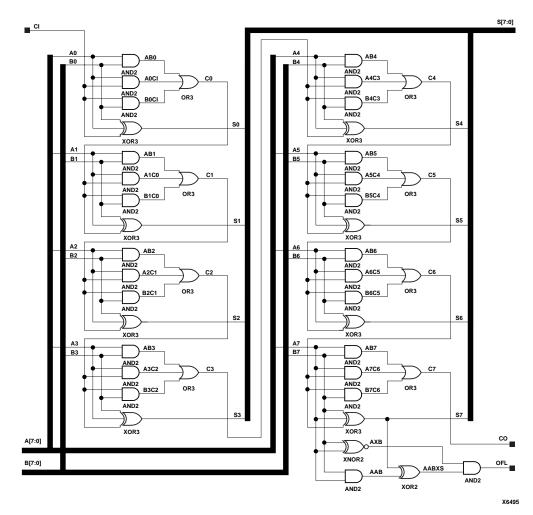

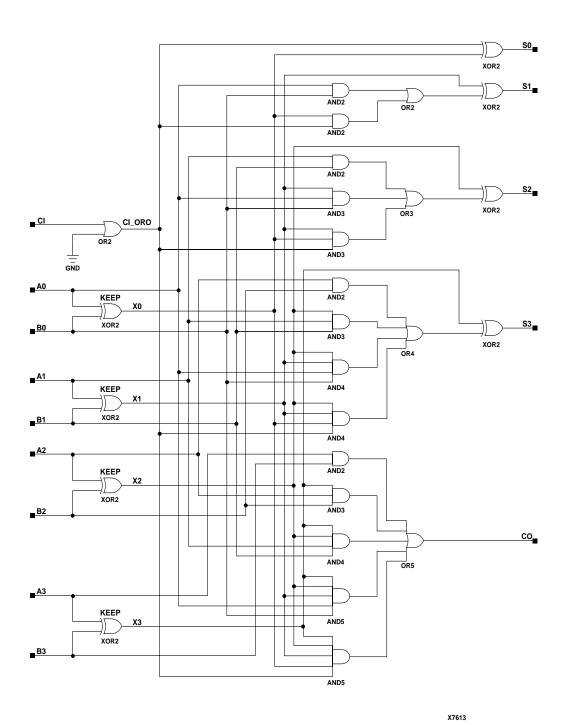

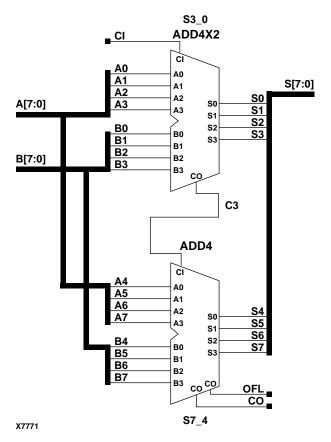

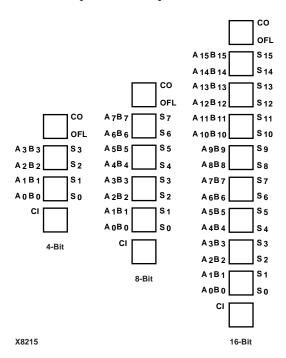

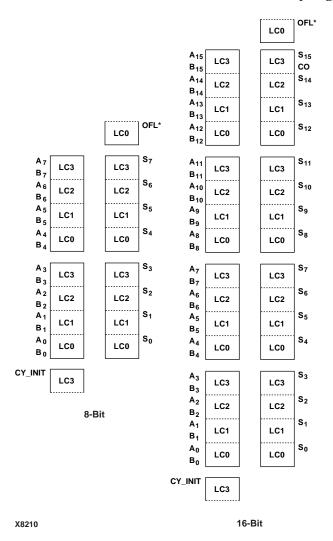

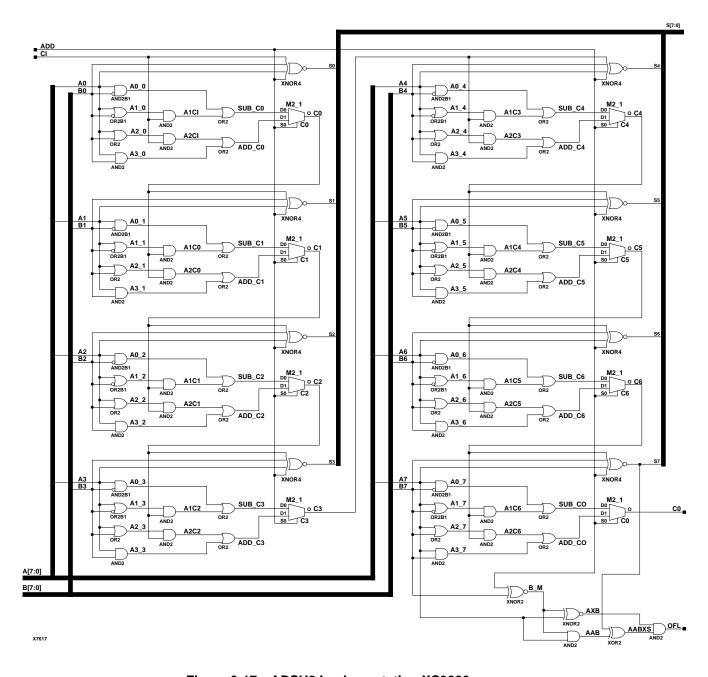

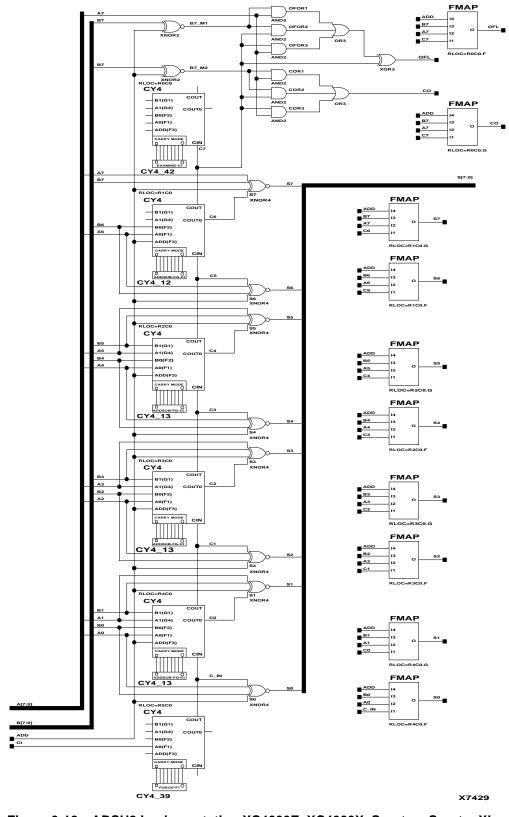

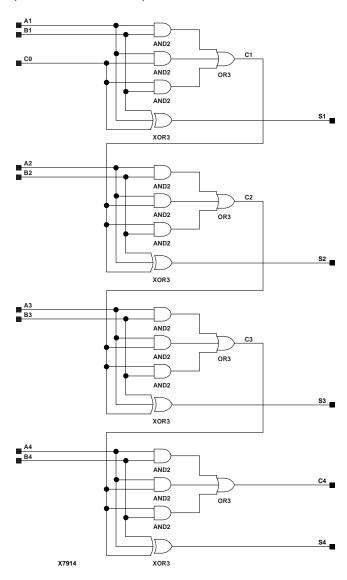

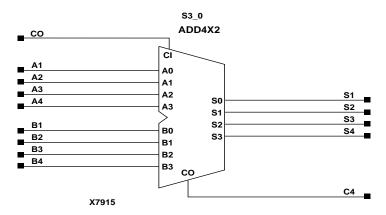

|           | ADD4, 8, 16                                                                         |        |

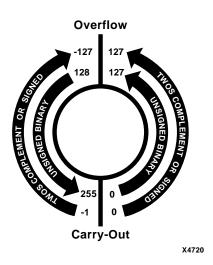

|           | 4-, 8-, 16-Bit Cascadable Full Adders with Carry-In, Carry-Out, and Overflow        |        |

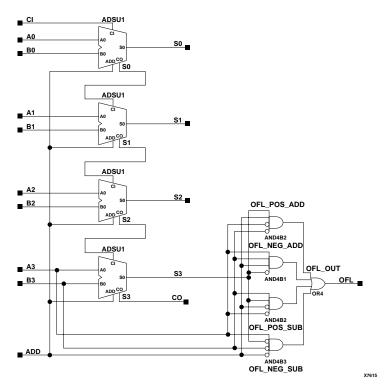

|           | ADSU1                                                                               |        |

|           | 1-Bit Cascadable Adder/Subtracter with Carry-In and Carry-Out                       |        |

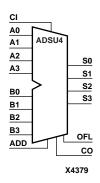

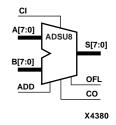

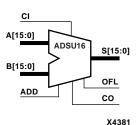

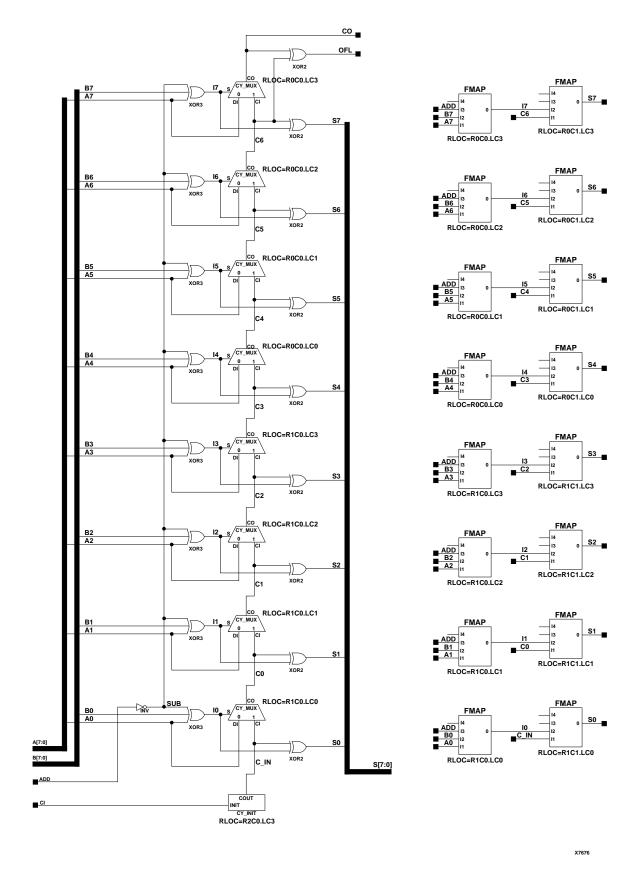

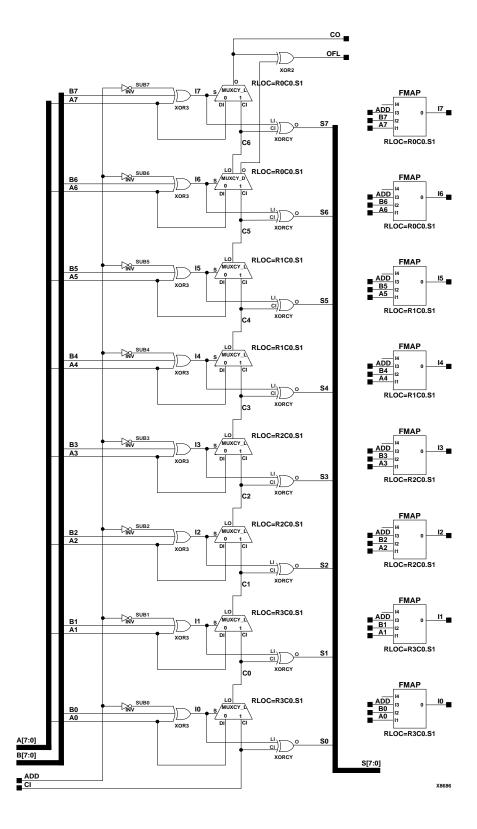

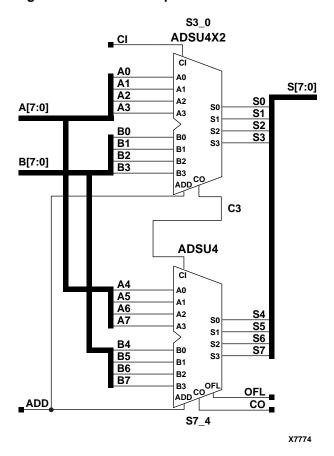

|           | ADSU4, 8, 16                                                                        |        |

|           | 4-, 8-, 16-Bit Cascadable Adders/Subtracters with Carry-In, Carry-Out, and Overflow |        |

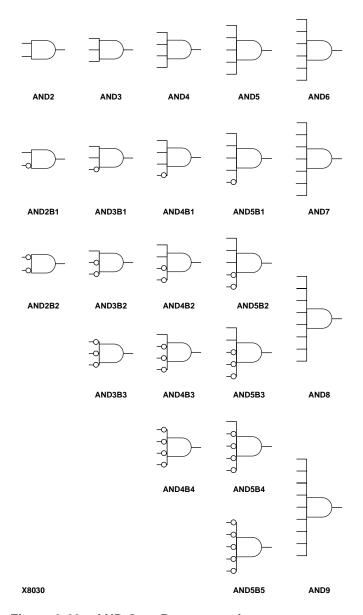

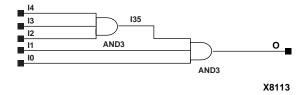

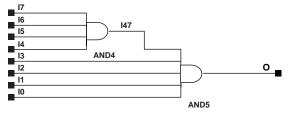

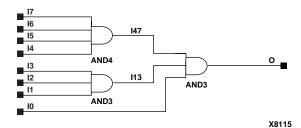

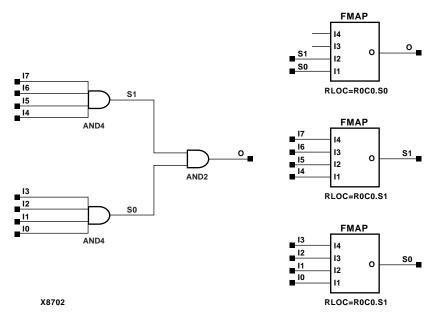

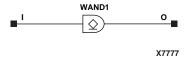

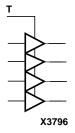

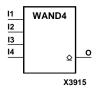

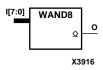

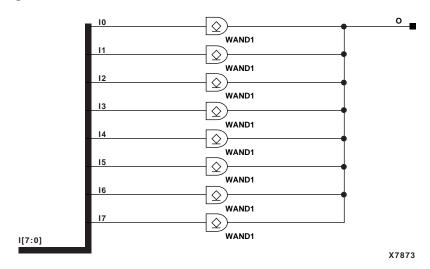

|           | AND2-9                                                                              |        |

|           | 2- to 9-Input AND Gates with Inverted and Non-Inverted Inputs                       |        |

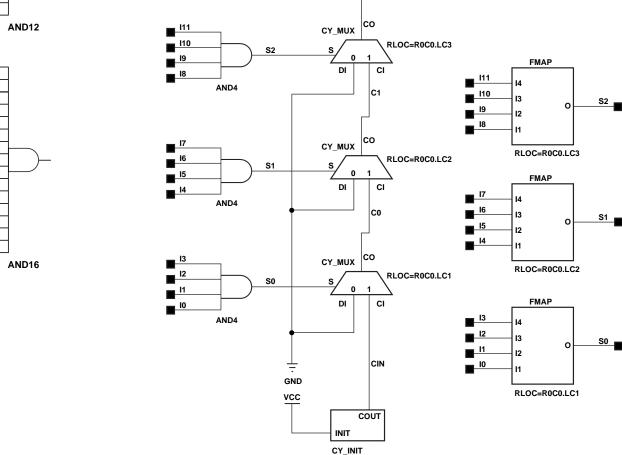

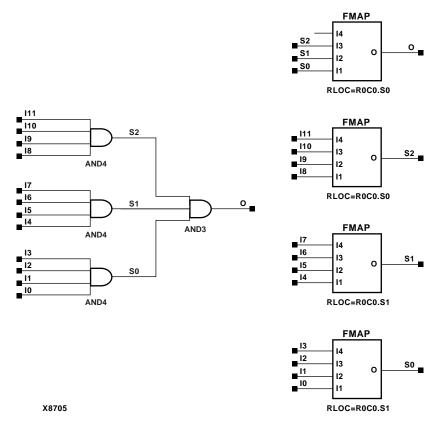

|           | AND12, 16                                                                           |        |

|           | 12- and 16-Input AND Gates with Non-Inverted Inputs                                 |        |

|           |                                                                                     |        |

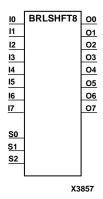

|           | BRLSHFT4, 8                                                                         |        |

|           | 4-, 8-Bit Barrel Shifters                                                           |        |

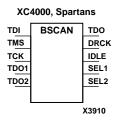

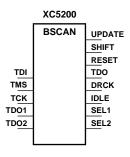

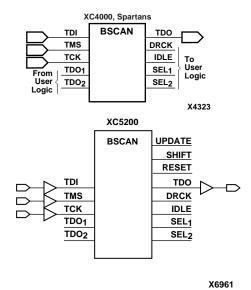

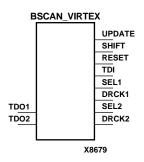

|           | BSCAN                                                                               |        |

|           | Boundary Scan Logic Control Circuit                                                 |        |

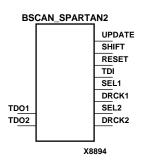

|           | BSCAN_SPARTAN2                                                                      |        |

|           | Spartan2 Boundary Scan Logic Control Circuit                                        |        |

|           | BSCAN_VIRTEX                                                                        |        |

|           | Virtex Boundary Scan Logic Control Circuit                                          |        |

|           | BUF                                                                                 |        |

|           | General-Purpose Buffer                                                              |        |

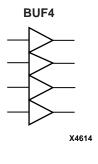

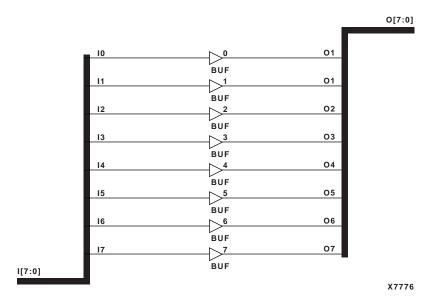

|           | BUF4, 8, 16                                                                         |        |

|           | General-Purpose Buffers                                                             | . 3-49 |

|           | BUFCF                                                                               |        |

|           | Fast Connect Buffer                                                                 | . 3-50 |

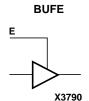

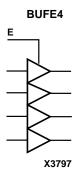

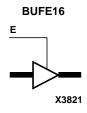

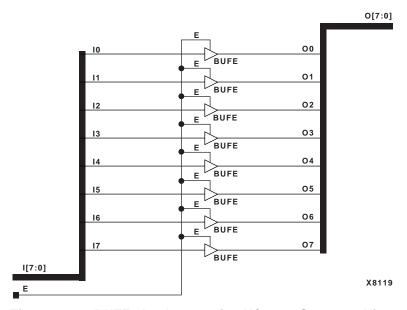

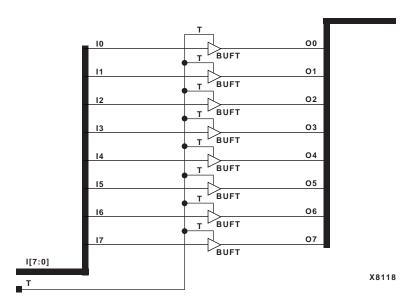

|           | BUFE, 4, 8, 16                                                                      | . 3-51 |

|           | Internal 3-State Buffers with Active High Enable                                    | . 3-51 |

|           | BUFFCLK                                                                             | . 3-53 |

|           | Global Fast Clock Buffer                                                            | . 3-53 |

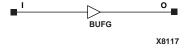

|           | BUFG                                                                                | . 3-54 |

|           | Clobal Clock Buffer                                                                 | 2 5/   |

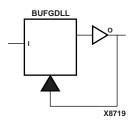

|           | BUFGDLL                                                                               | 3-55 |

|-----------|---------------------------------------------------------------------------------------|------|

|           | Clock Delay Locked Loop Buffer                                                        |      |

|           | BUFGE                                                                                 |      |

|           | Global Low Early Clock Buffer                                                         | 3-56 |

|           | BUFGLS                                                                                |      |

|           | Global Low Skew Clock Buffer                                                          | 3-57 |

|           | BUFGP                                                                                 |      |

|           | Primary Global Buffer for Driving Clocks or Longlines (Four per PLD Device)           |      |

|           | BUFGS                                                                                 |      |

|           | Secondary Global Buffer for Driving Clocks or Longlines (Four per PLD Device)         |      |

|           | BUFGSR                                                                                |      |

|           | Global Set/Reset Input Buffer                                                         |      |

|           | BUFGTS                                                                                |      |

|           | Global Three-State Input Buffer                                                       |      |

|           | BUFOD                                                                                 |      |

|           | Open-Drain Buffer                                                                     |      |

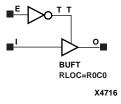

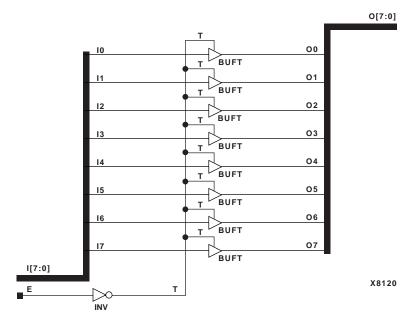

|           | BUFT, 4, 8, 16Internal 3-State Buffers with Active-Low Enable                         |      |

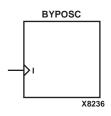

|           | BYPOSC                                                                                |      |

|           | Bypass Oscillator                                                                     |      |

|           |                                                                                       | 5-05 |

| Chapter 4 | Design Elements (CAPTURE_SPARTAN2 to DECODE64)                                        |      |

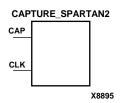

|           | CAPTURE_SPARTAN2                                                                      | 4-2  |

|           | Spartan2 Register State Capture for Bitstream Readback                                |      |

|           | CAPTURE_VIRTEX                                                                        |      |

|           | Virtex Register State Capture for Bitstream Readback                                  | 4-3  |

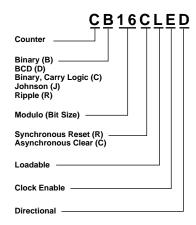

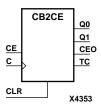

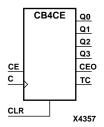

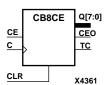

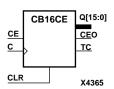

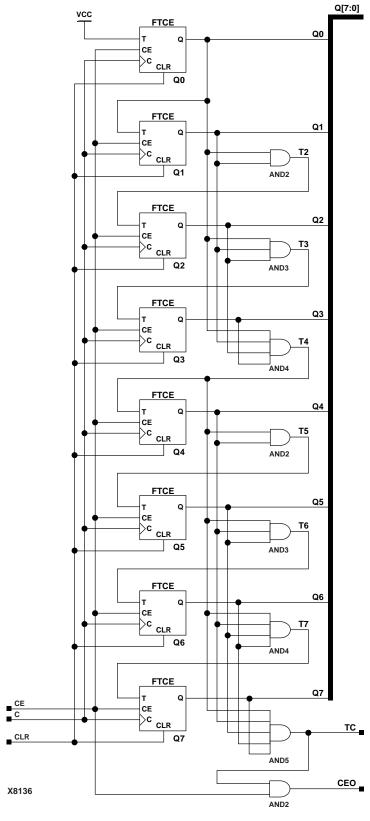

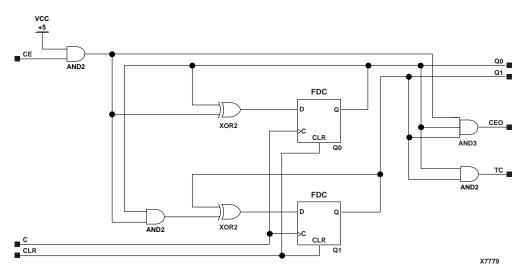

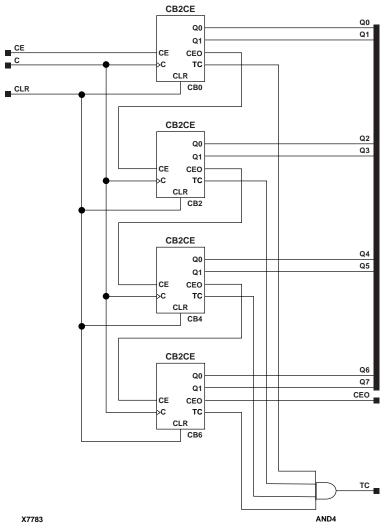

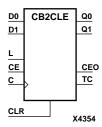

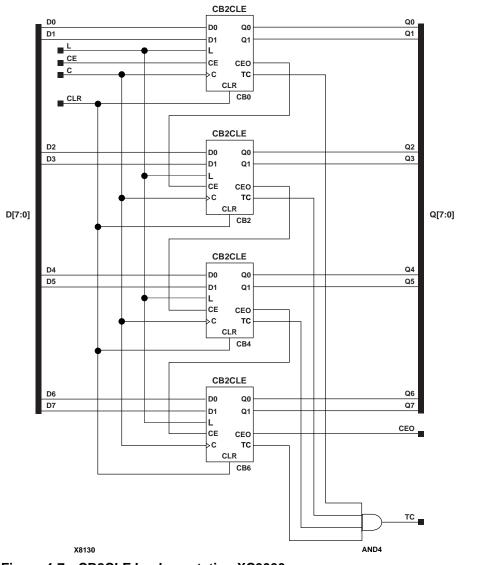

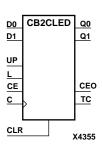

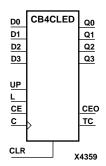

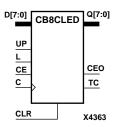

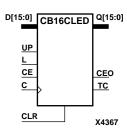

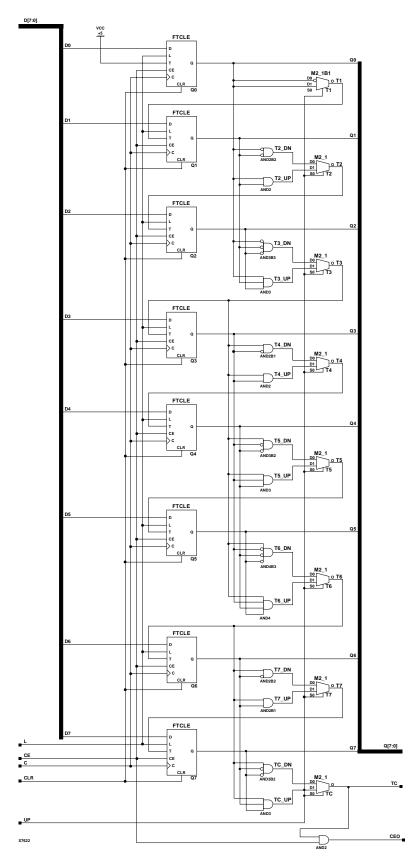

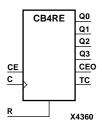

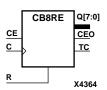

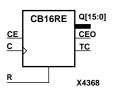

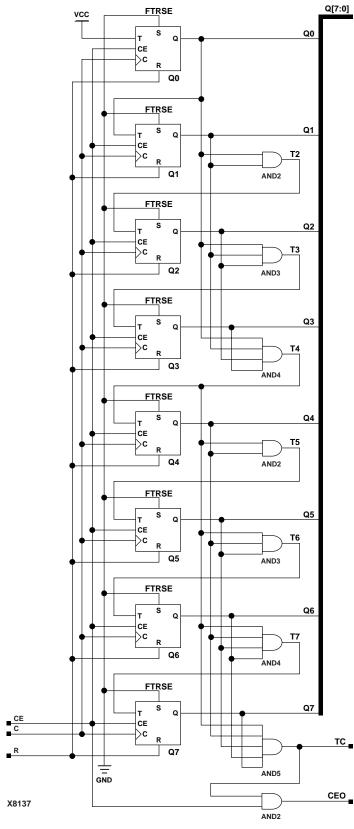

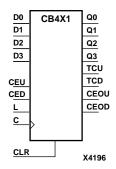

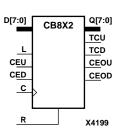

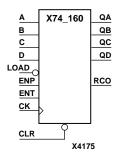

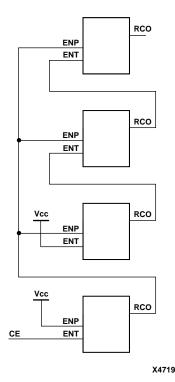

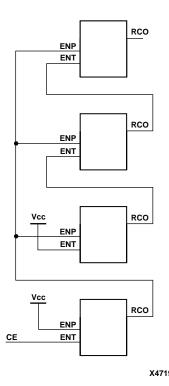

|           | CB2CE, CB4CE, CB8CE, CB16CE                                                           | 4-4  |

|           | 2-, 4-, 8-,16-Bit Cascadable Binary Counters with Clock Enable and Asynchronous Clear | 4-4  |

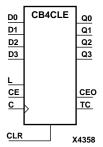

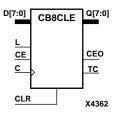

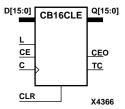

|           | CB2CLE, CB4CLE, CB8CLE, CB16CLE                                                       |      |

|           | 2-, 4-, 8-, 16-Bit Loadable Cascadable Binary Counters with Clock Enable and          |      |

|           | Asynchronous Clear                                                                    | 4-7  |

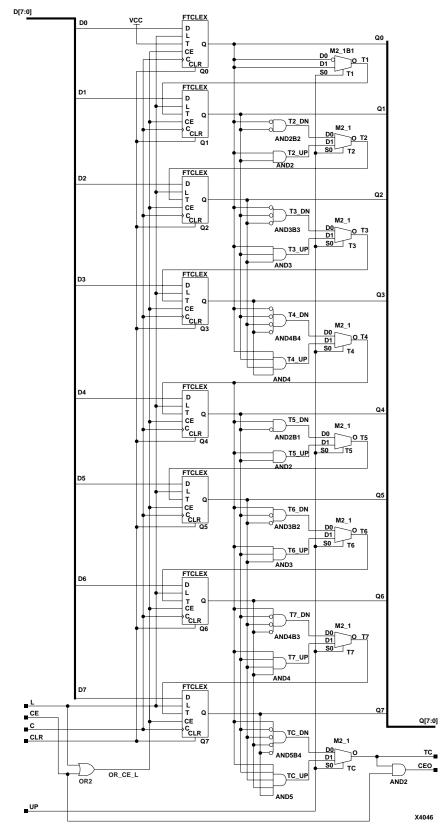

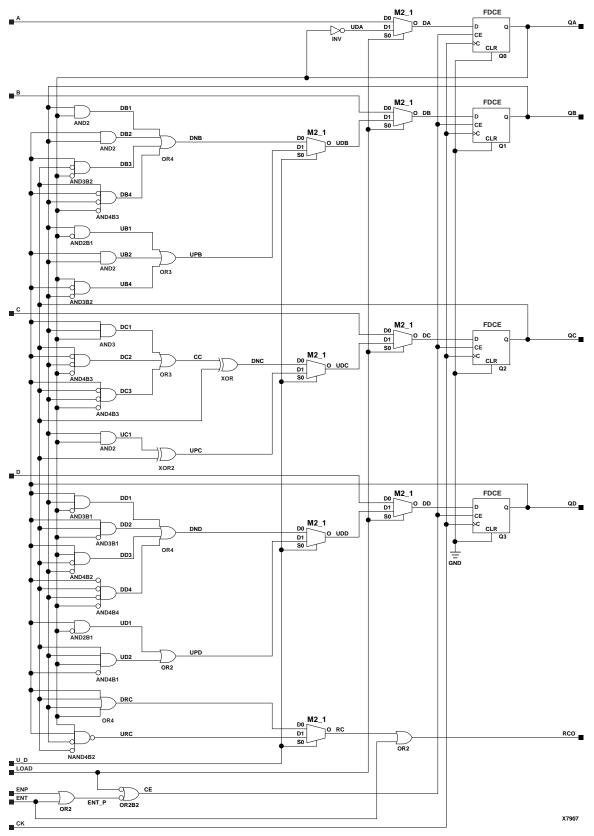

|           | CB2CLED, CB4CLED, CB8CLED, CB16CLED                                                   |      |

|           | 2-, 4-, 8-, 16-Bit Loadable Cascadable Bidirectional Binary Counters with Clock       |      |

|           | Enable and Asynchronous Clear                                                         | 4-11 |

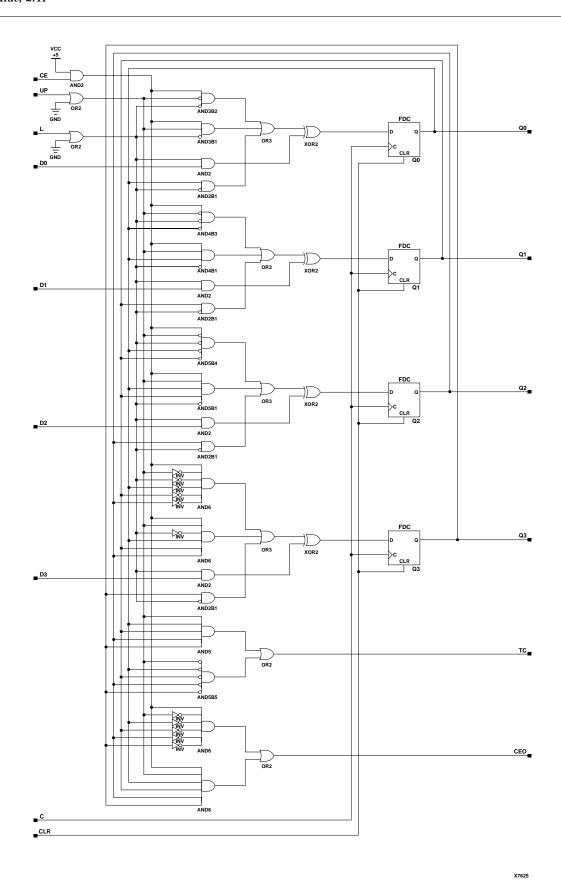

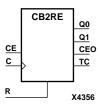

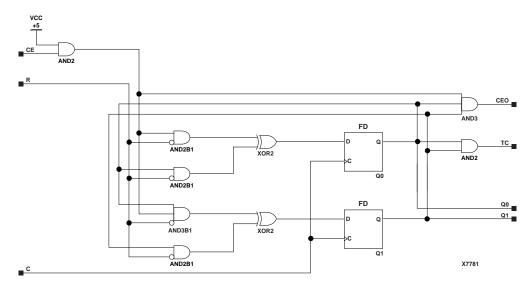

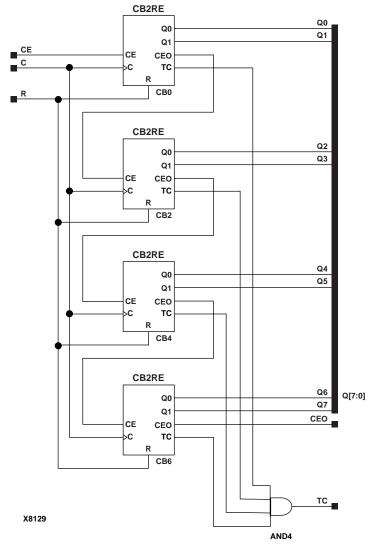

|           | CB2RE, CB4RE, CB8RE, CB16RE                                                           | 4-15 |

|           | 2-, 4-, 8-, 16-Bit Cascadable Binary Counters with Clock Enable and Synchronous       |      |

|           | Reset                                                                                 |      |

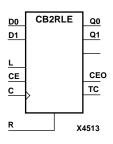

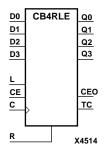

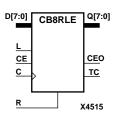

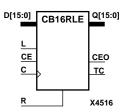

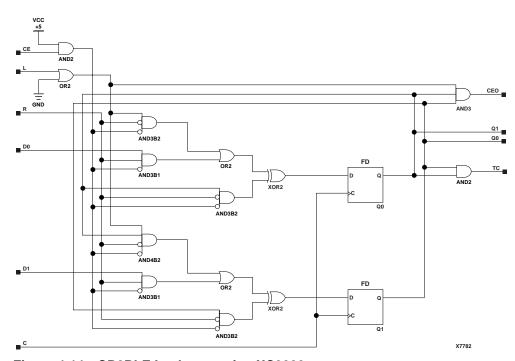

|           | CB2RLE, CB4RLE, CB8RLE, CB16RLE                                                       | 4-18 |

|           | 2-, 4-, 8-, 16-Bit Loadable Cascadable Binary Counters with Clock Enable and          |      |

|           | Synchronous Reset                                                                     |      |

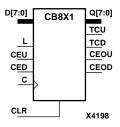

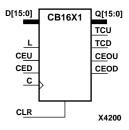

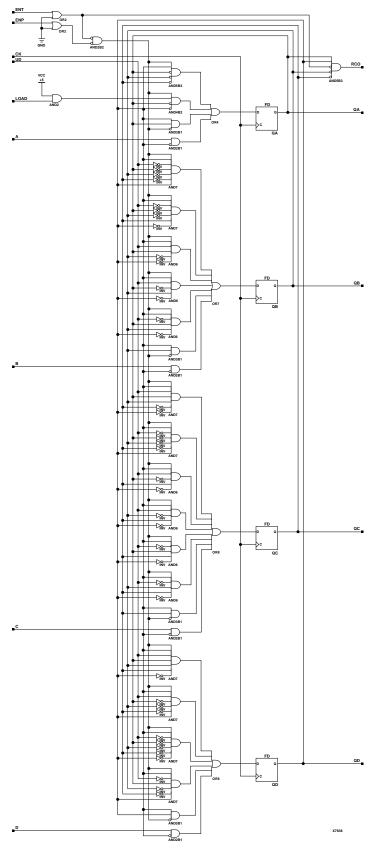

|           | CB2X1, CB4X1, CB8X1, CB16X1                                                           | 4-20 |

|           | 2-, 4-, 8-, 16-Bit Loadable Cascadable Bidirectional Binary Counters with Clock       |      |

|           | Enable and Asynchronous Clear                                                         |      |

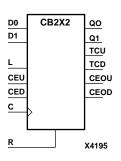

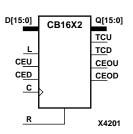

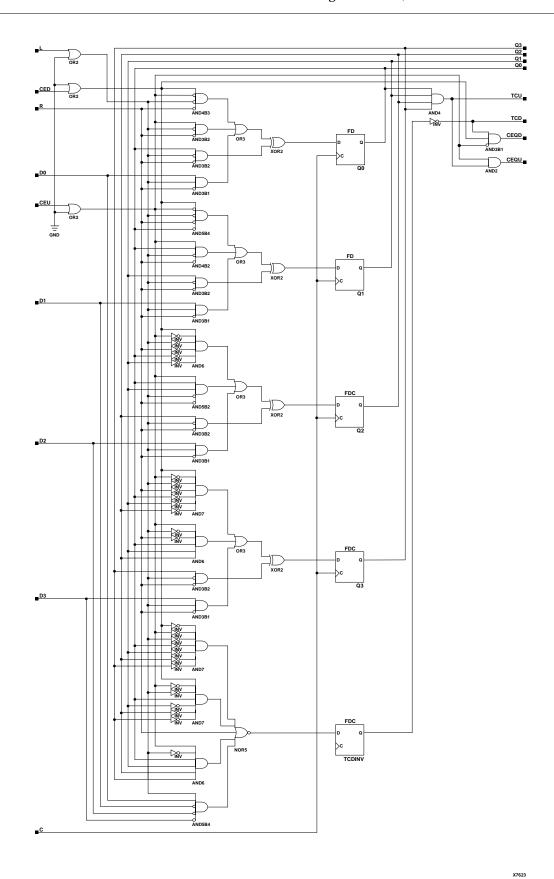

|           | CB2X2, CB4X2, CB8X2, CB16X2                                                           | 4-23 |

|           | 2-, 4-, 8-, and 16-Bit Loadable Cascadable Bidirectional Binary Counters with Clock   | 4.00 |

|           | Enable and Synchronous Reset                                                          |      |

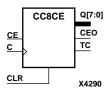

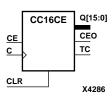

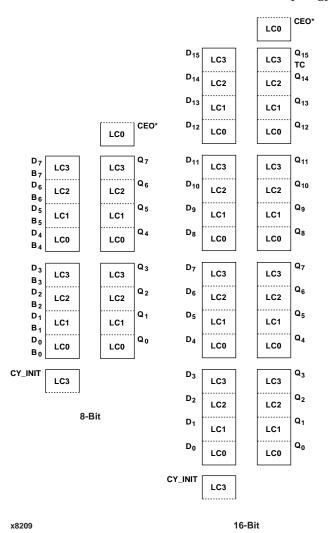

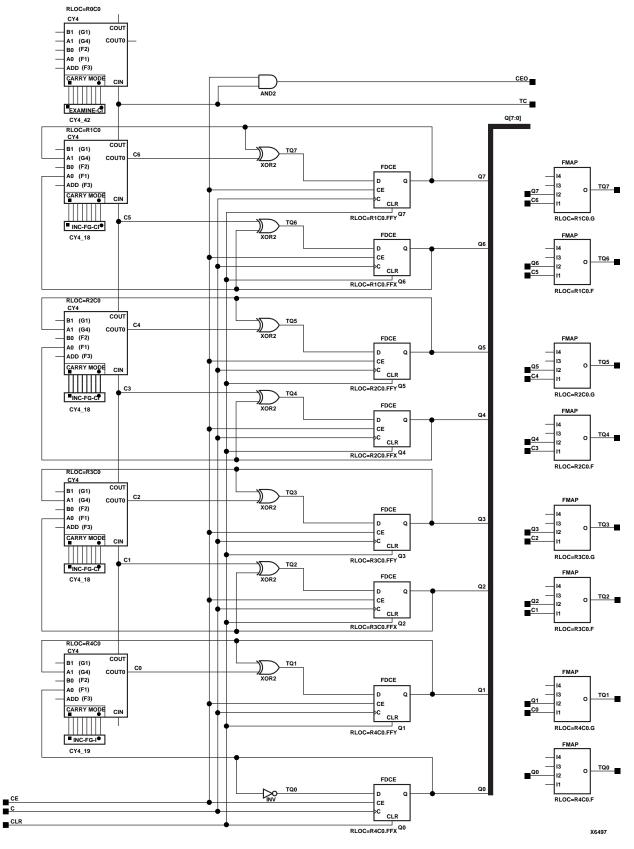

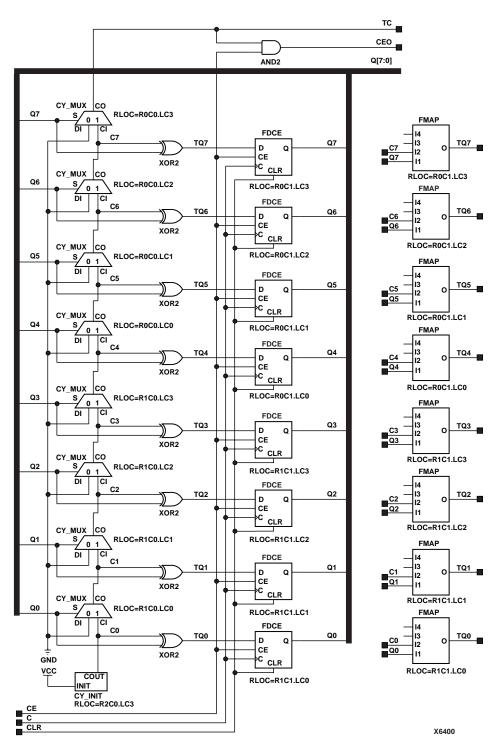

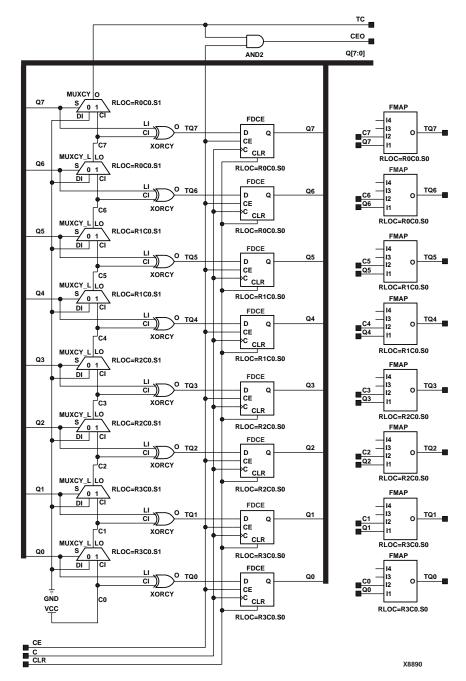

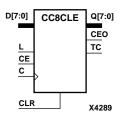

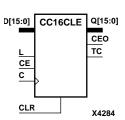

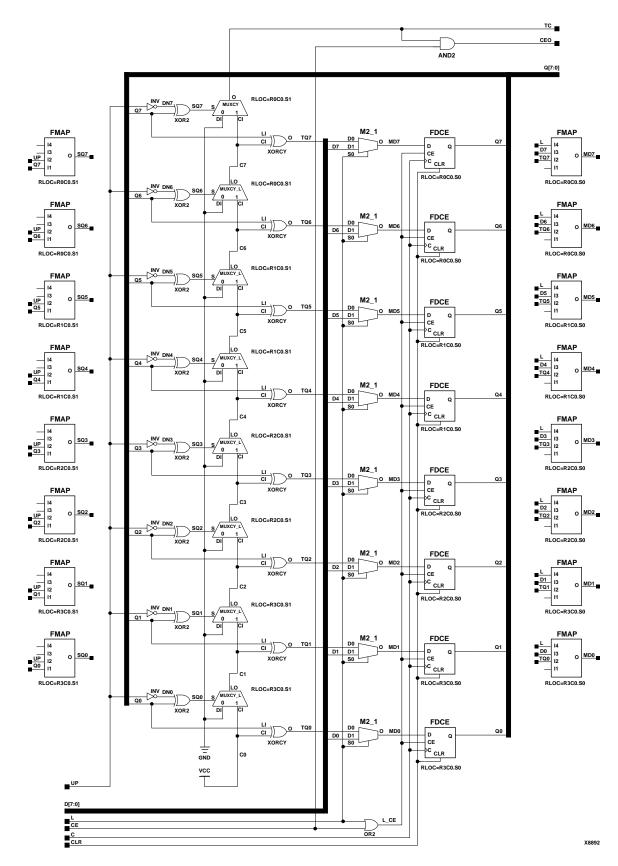

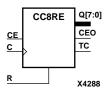

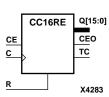

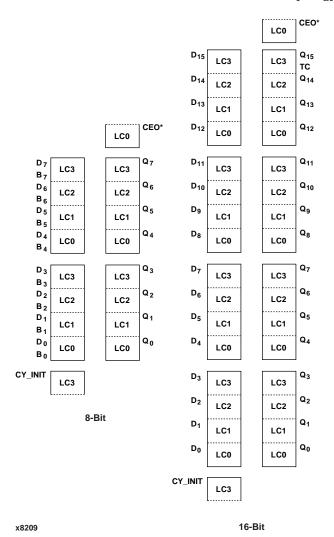

|           | CC8CE, CC16CE                                                                         |      |

|           | CC8CLE, CC16CLECC8CLE                                                                 |      |

|           | 8-, 16-Bit Loadable Cascadable Binary Counters with Clock Enable and                  | 4-32 |

|           | Asynchronous Cloar                                                                    | 4-32 |

Libraries Guide, 2.1i

| CC8CLED, CC16CLED                                                                  | 4-38         |

|------------------------------------------------------------------------------------|--------------|

| 8-, 16-Bit Loadable Cascadable Bidirectional Binary Counters with Clock Enable and |              |

| Asynchronous Clear                                                                 | 4-38         |

| CC8RÉ, CC16RE                                                                      | 4-44         |

| 8-, 16-Bit Cascadable Binary Counters with Clock Enable and Synchronous Reset      | 4-44         |

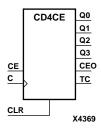

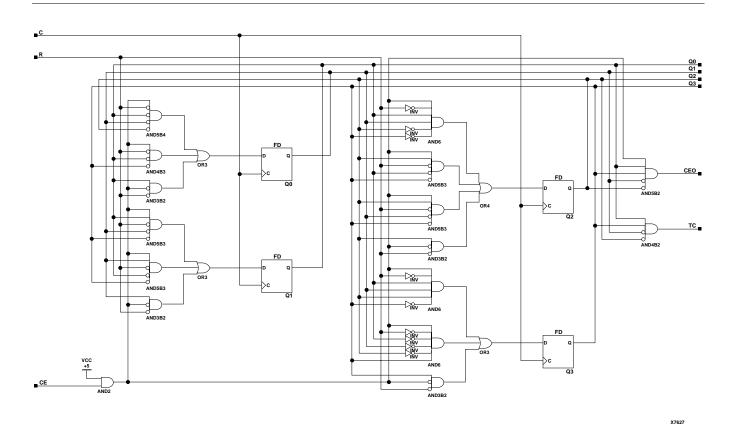

| CD4CE                                                                              | 4-50         |

| 4-Bit Cascadable BCD Counter with Clock Enable and Asynchronous Clear              | 4-50         |

| CD4CLE                                                                             | 4-53         |

| 4-Bit Loadable Cascadable BCD Counter with Clock Enable and Asynchronous Clear     | 4-53         |

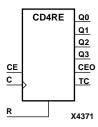

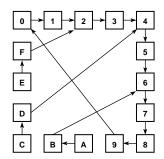

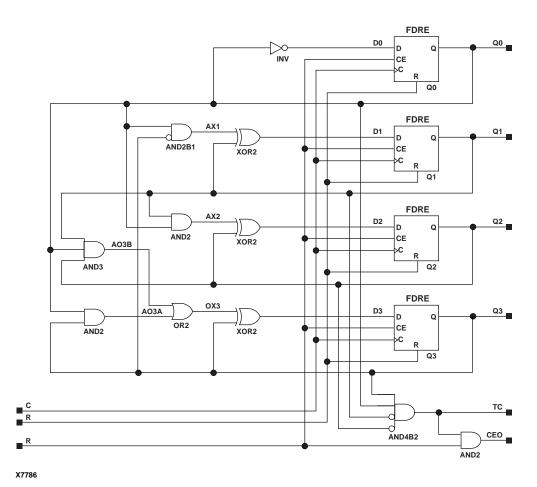

| CD4RE                                                                              | 4-56         |

| 4-Bit Cascadable BCD Counter with Clock Enable and Synchronous Reset               | 4-56         |

|                                                                                    | 4-59         |

| CD4RLE                                                                             |              |

| 4-Bit Loadable Cascadable BCD Counter with Clock Enable and Synchronous Reset .    |              |

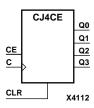

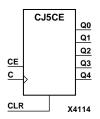

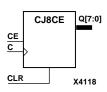

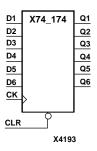

| CJ4CE, CJ5CE, CJ8CE                                                                | 4-62         |

| 4-, 5-, 8-Bit Johnson Counters with Clock Enable and Asynchronous Clear            | 4-62         |

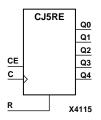

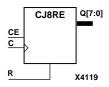

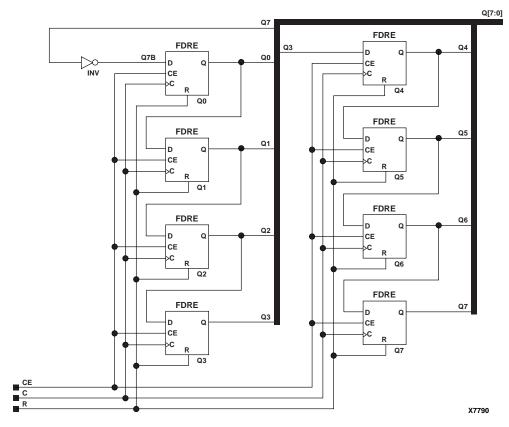

| CJ4RE, CJ5RE, CJ8RE                                                                | 4-64         |

| 4-, 5-, 8-Bit Johnson Counters with Clock Enable and Synchronous Reset             | 4-64         |

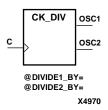

| CK_DIV                                                                             |              |

| Internal Multiple-Frequency Clock Divider                                          | 4-66         |

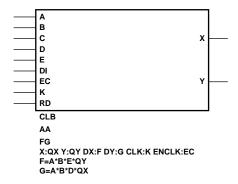

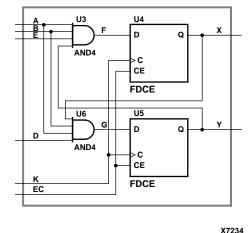

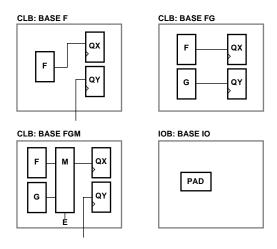

| CLB                                                                                | 4-67         |

| CLB Configuration Symbol                                                           | 4-67         |

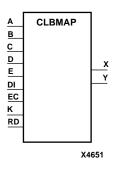

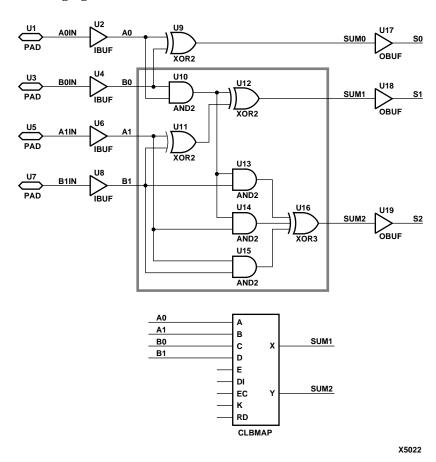

| CLBMAP                                                                             | 4-69         |

| Logic-Partitioning Control Symbol                                                  | 4-69         |

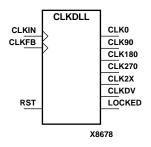

| CLKDLL                                                                             | 4-71         |

| Clock Delay Locked Loop                                                            | 4-71         |

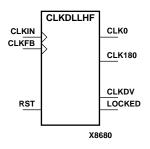

| CLKDLLHF                                                                           | 4-73         |

| High Frequency Clock Delay Locked Loop                                             |              |

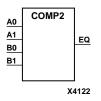

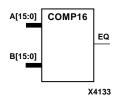

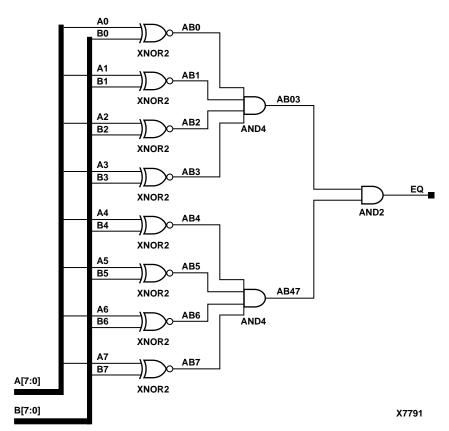

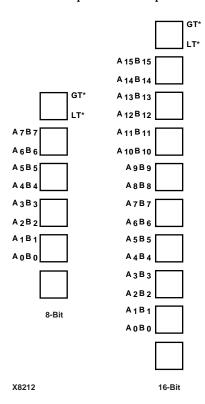

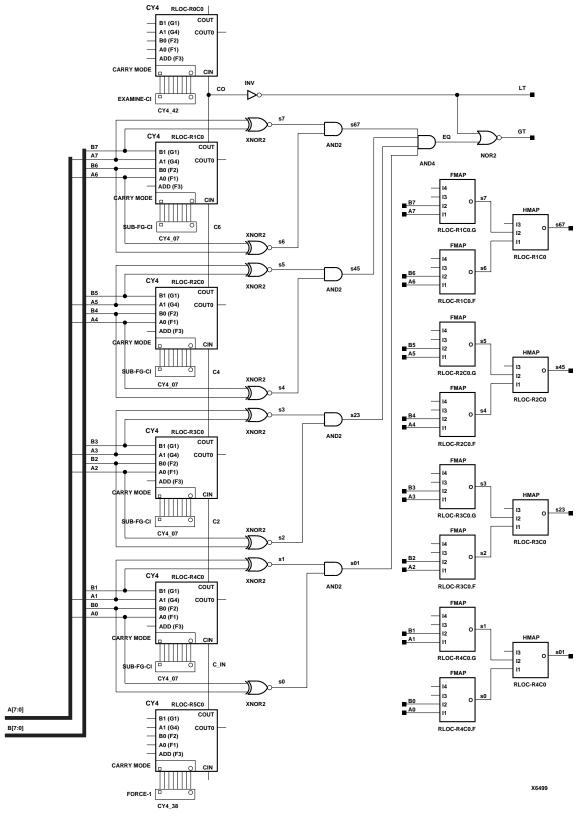

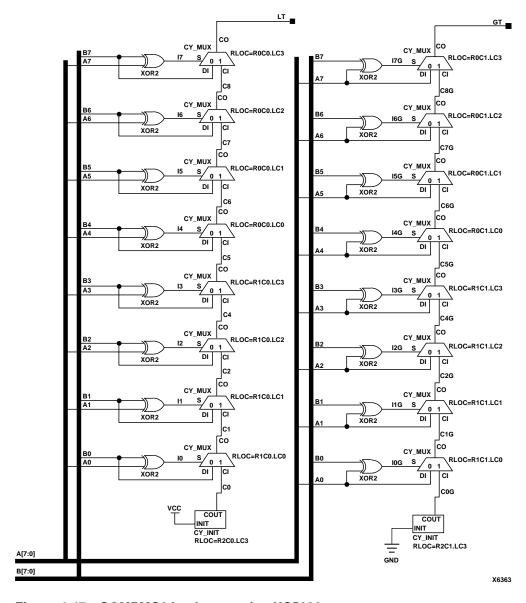

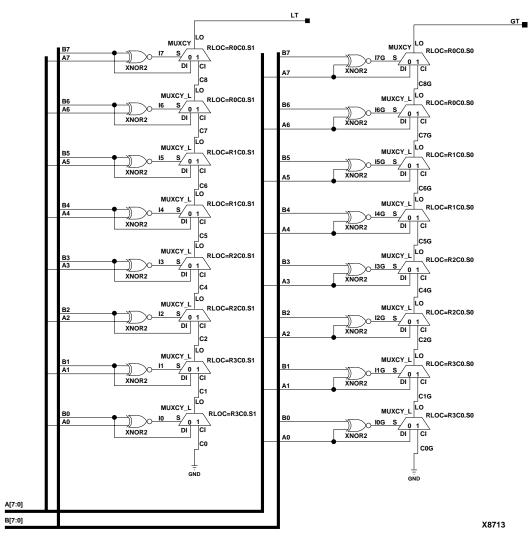

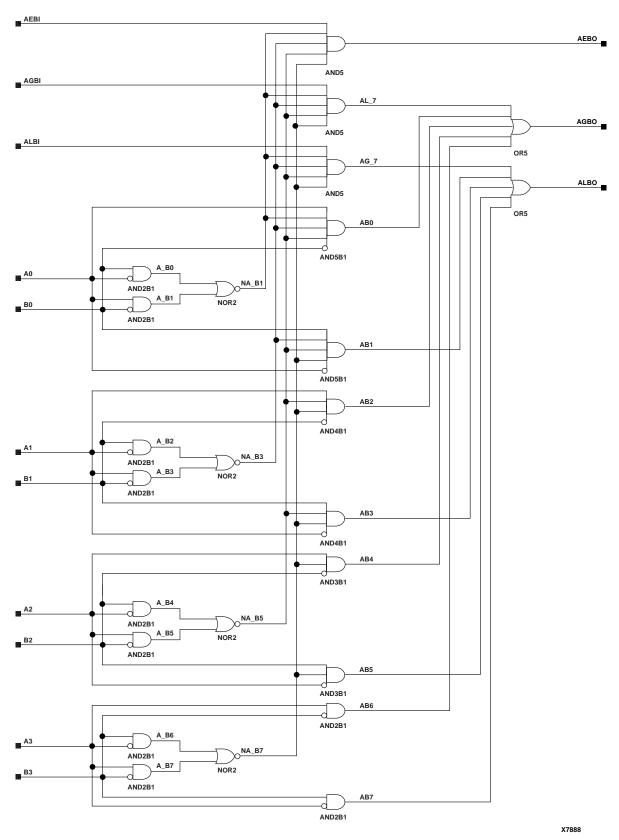

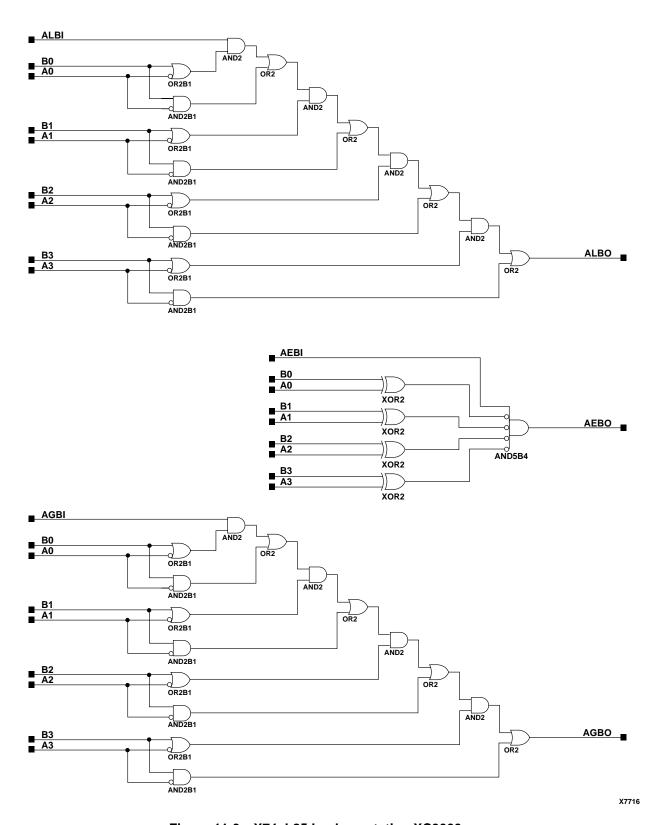

| COMP2, 4, 8, 16                                                                    | 4-74         |

| 2-, 4-, 8-, 16-Bit Identity Comparators                                            | 4-74         |

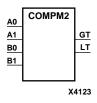

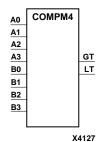

| COMPM2, 4, 8, 16                                                                   | 4-75         |

| 2-, 4-, 8-, 16-Bit Magnitude Comparators                                           | 4-75         |

| · · · · · · · · · · · · · · · · · · ·                                              | 4-75<br>4-79 |

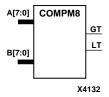

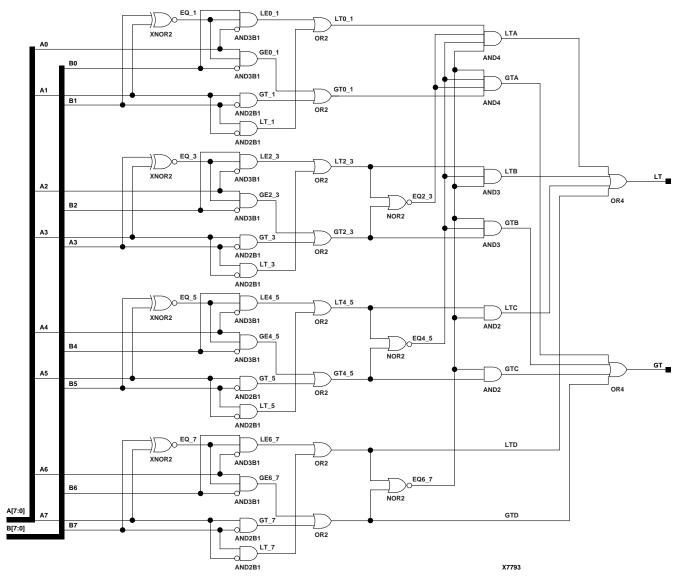

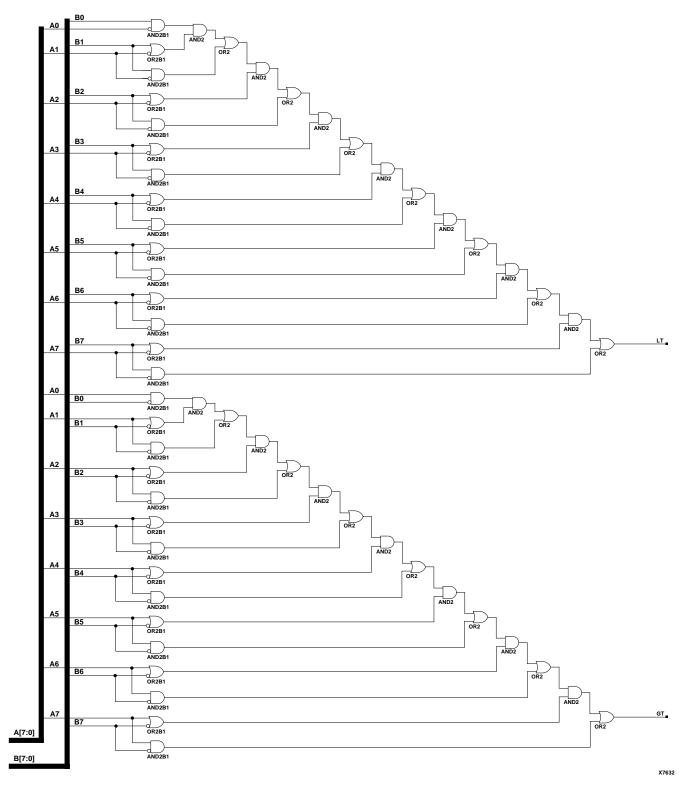

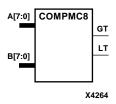

| COMPMC8, 16                                                                        |              |

| 8-, 16-Bit Magnitude Comparators                                                   | 4-79         |

| CONFIG                                                                             | _            |

| Repository for Schematic-Level (Global) Attributes                                 | 4-84         |

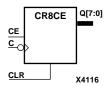

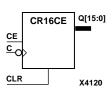

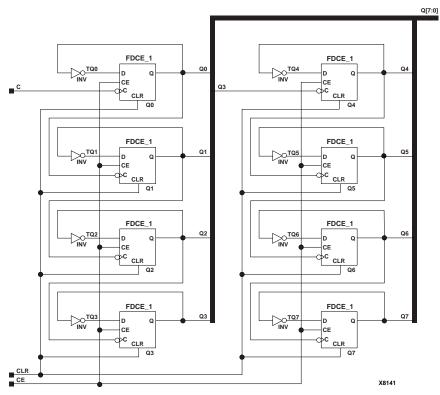

| CR8CE, CR16CE                                                                      | 4-85         |

| 8-, 16-Bit Negative-Edge Binary Ripple Counters with Clock Enable and              |              |

| Asynchronous Clear                                                                 |              |

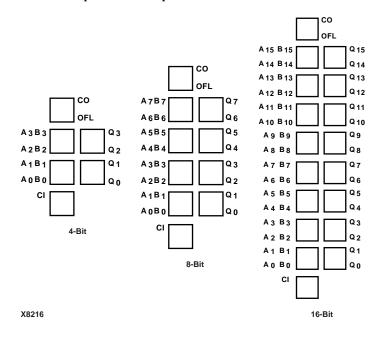

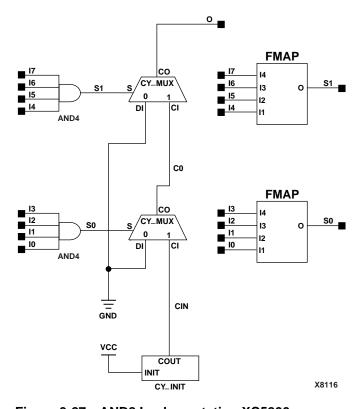

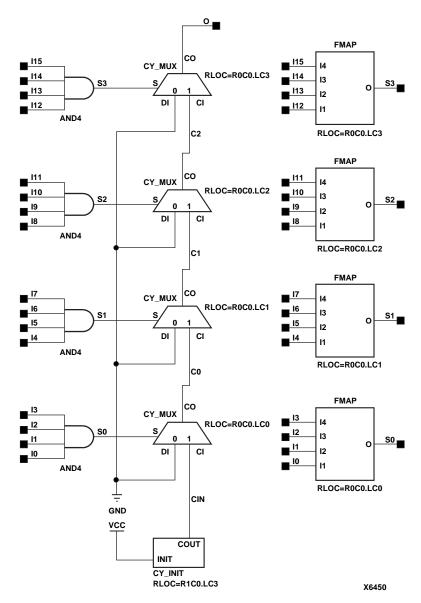

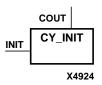

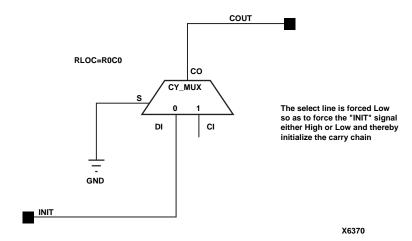

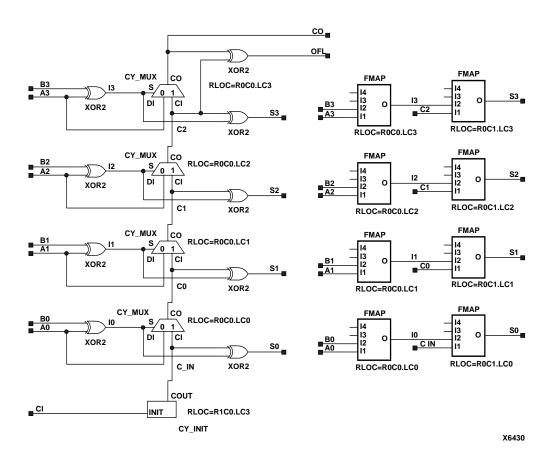

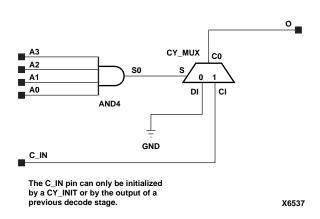

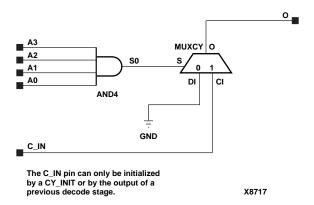

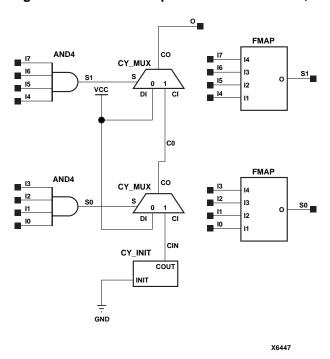

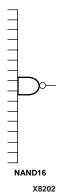

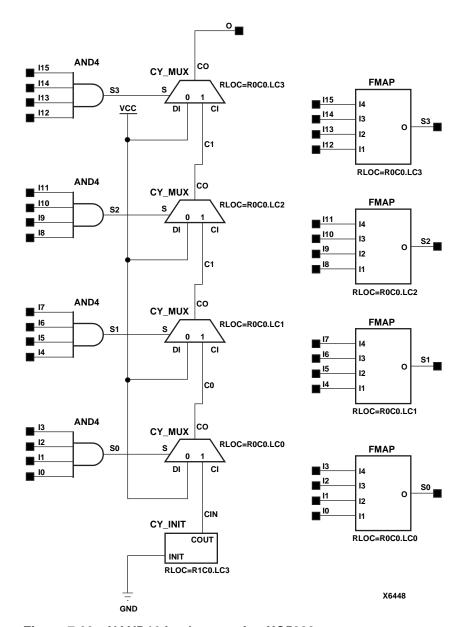

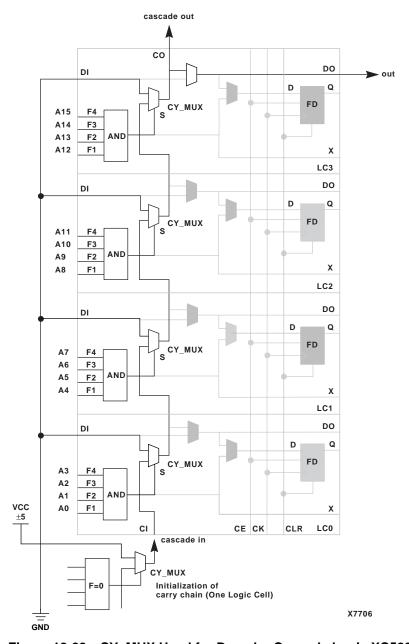

| CY_INIT                                                                            |              |

| Initialization Stage for Carry Chain                                               | 4-88         |

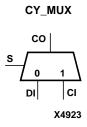

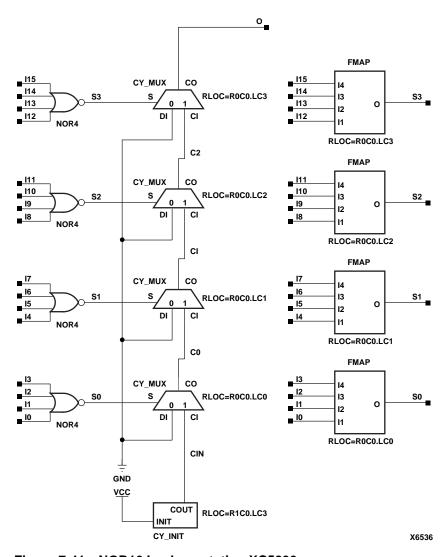

| CY_MUX                                                                             | 4-89         |

| 2-to-1 Multiplexer for Carry Logic                                                 | 4-89         |

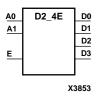

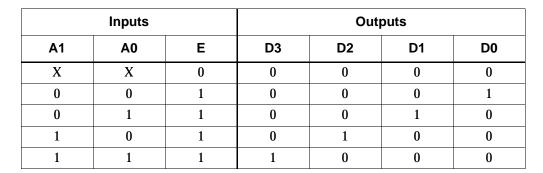

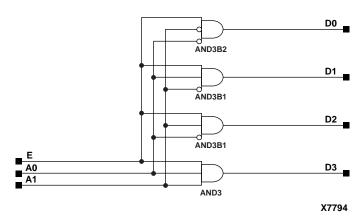

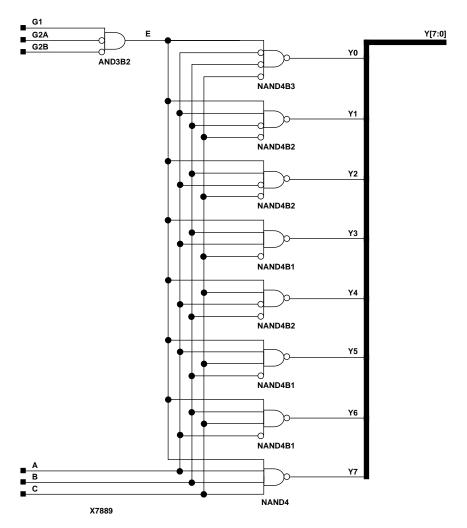

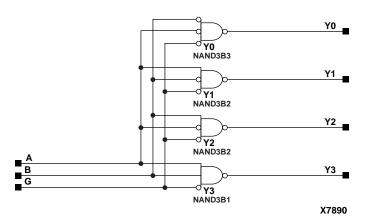

| D2_4E                                                                              |              |

| 2- to 4-Line Decoder/Demultiplexer with Enable                                     |              |

| D3_8E                                                                              |              |

| 3- to 8-Line Decoder/Demultiplexer with Enable                                     | 4-92         |

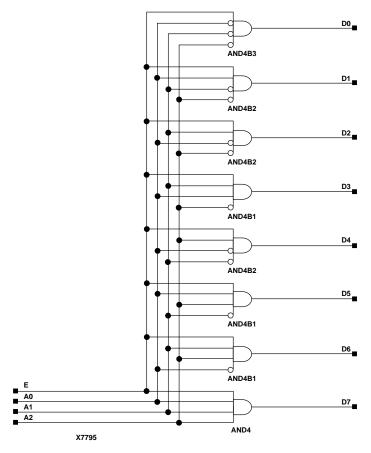

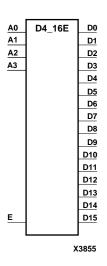

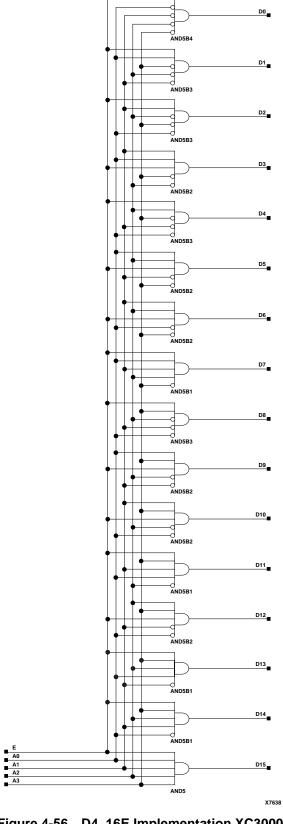

| D4_16E                                                                             |              |

| 4- to 16-Line Decoder/Demultiplexer with Enable                                    |              |

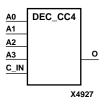

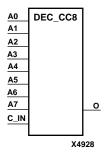

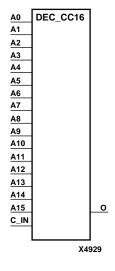

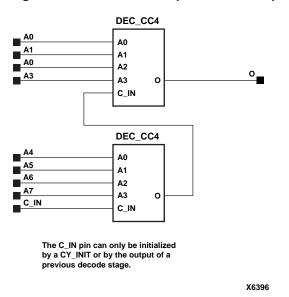

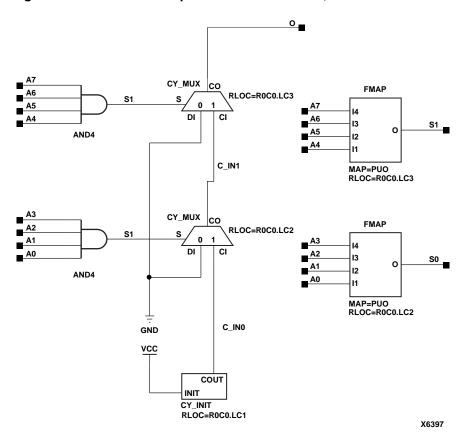

| DEC_CC4, 8, 16                                                                     |              |

| 4-, 8-, 16-Bit Active Low Decoders                                                 |              |

|                                                                                    |              |

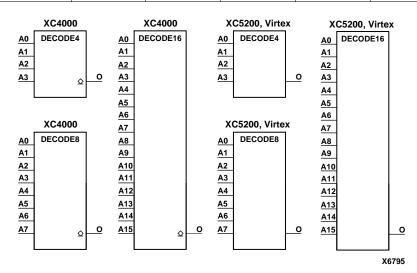

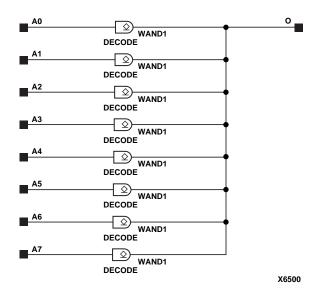

| DECODE4, 8, 16                                                                     |              |

| 4-, 8-, 16-Bit Active-Low Decoders                                                 |              |

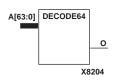

| DECODE32, 64                                                                       | 4-10<br>4-10 |

| az- and pa-bit active-Low Decoders                                                 | 4-111        |

# **Chapter 5** Design Elements (F5MAP to FTSRLE)

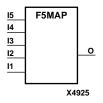

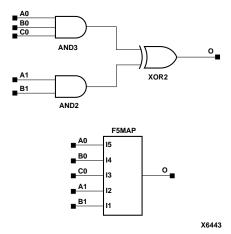

| F5MAP                                                                       | 5-2  |

|-----------------------------------------------------------------------------|------|

| 5-Input Function Partitioning Control Symbol                                | 5-2  |

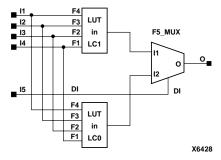

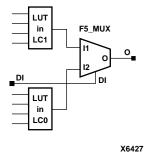

| F5_MUX                                                                      |      |

| 2-to-1 Lookup Table Multiplexer                                             | 5-3  |

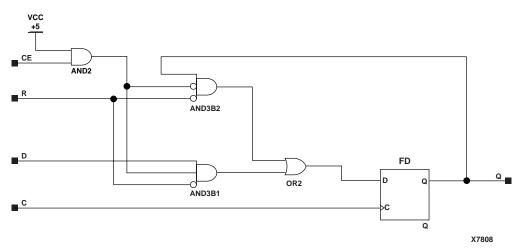

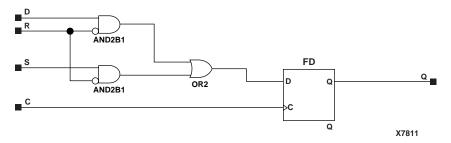

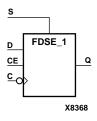

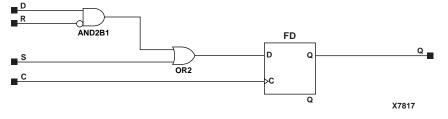

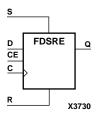

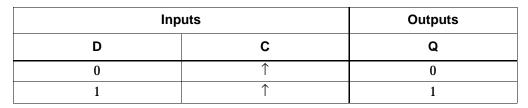

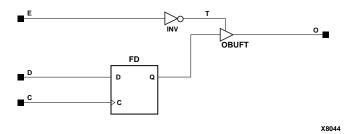

| FD                                                                          | 5-4  |

| D Flip-Flop                                                                 |      |

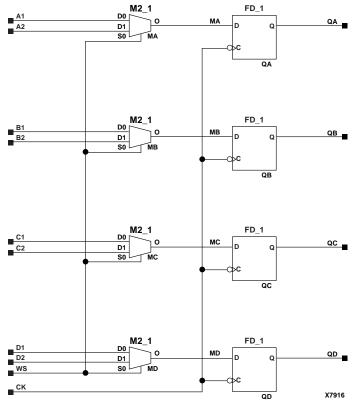

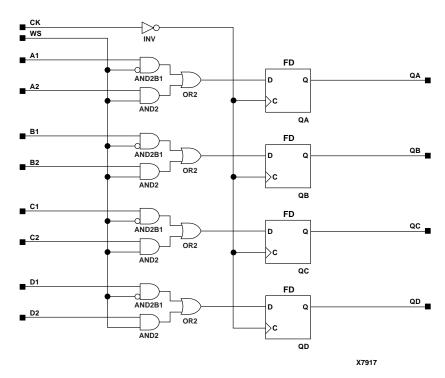

| FD 1                                                                        |      |

| D Flip-Flop with Negative-Edge Clock                                        |      |

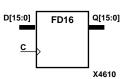

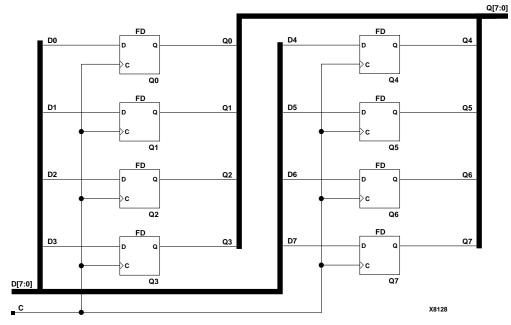

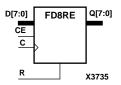

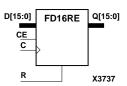

| FD4, 8, 16                                                                  |      |

| Multiple D Flip-Flops                                                       |      |

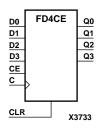

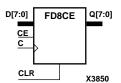

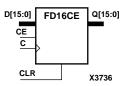

| FD4CE, FD8CE, FD16CE                                                        |      |

| 4-, 8-, 16-Bit Data Registers with Clock Enable and Asynchronous Clear      |      |

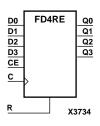

| FD4RE, FD8RE, FD16RE                                                        |      |

| 4-, 8-, 16-Bit Data Registers with Clock Enable and Synchronous Reset       | 5-10 |

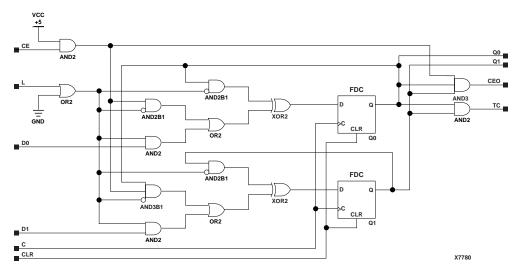

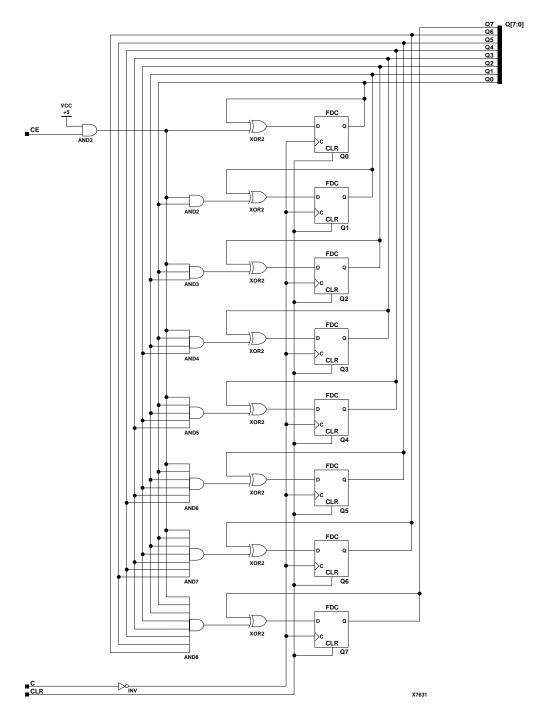

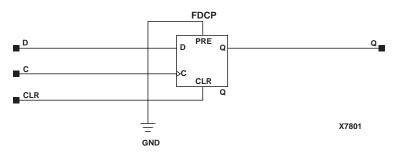

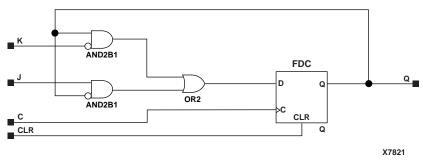

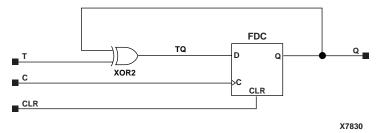

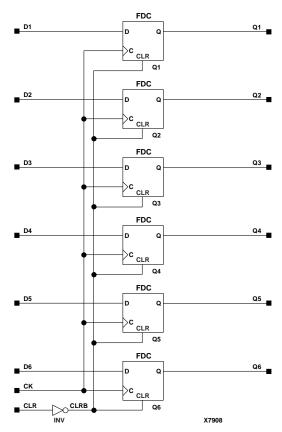

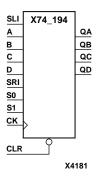

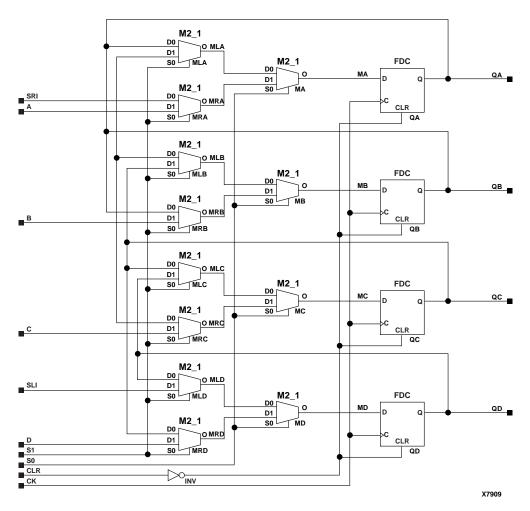

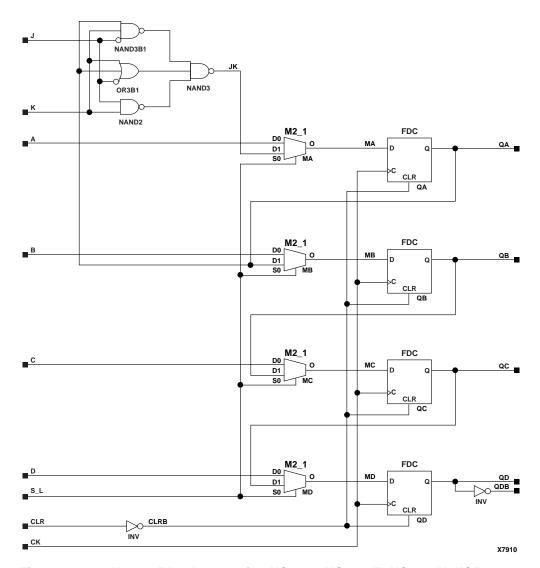

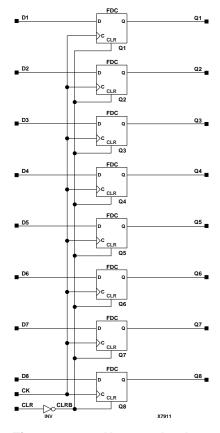

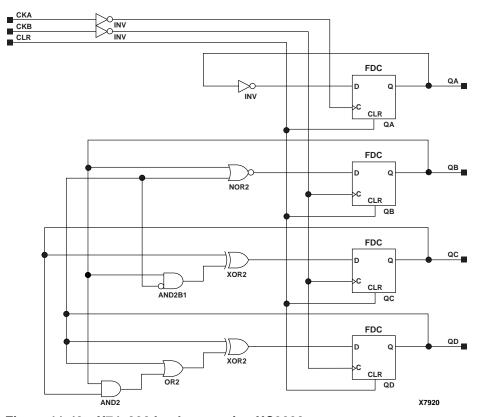

| FDC                                                                         | 5-10 |

|                                                                             |      |

| D Flip-Flop with Asynchronous Clear                                         |      |

| FDC_1                                                                       |      |

| D Flip-Flop with Negative-Edge Clock and Asynchronous Clear                 |      |

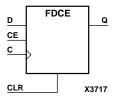

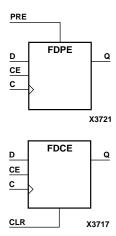

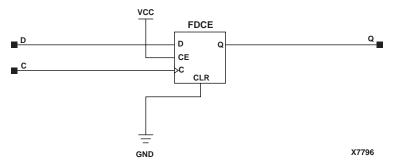

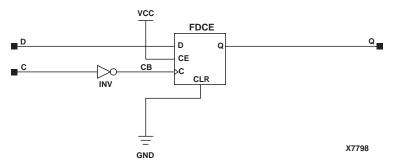

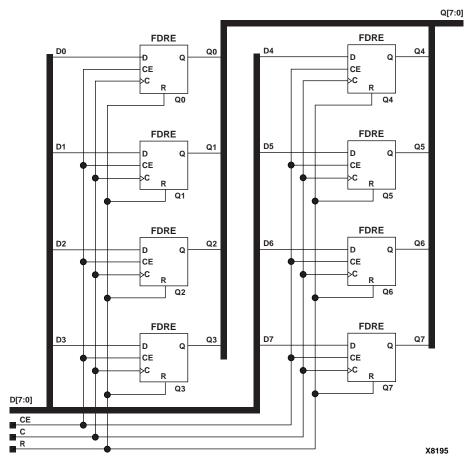

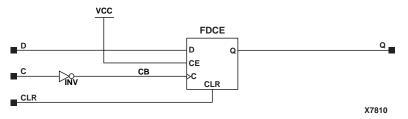

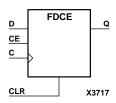

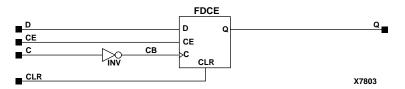

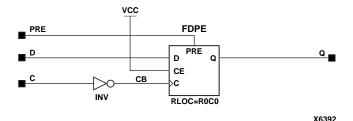

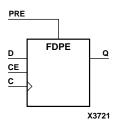

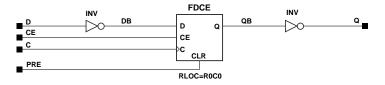

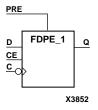

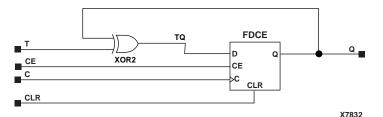

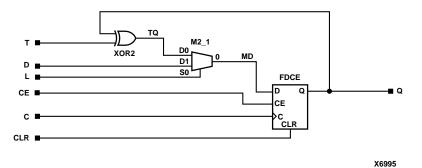

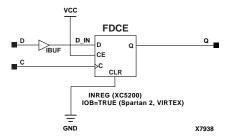

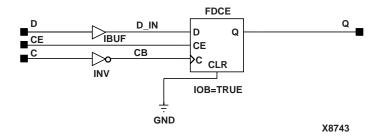

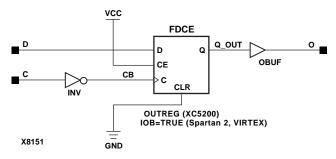

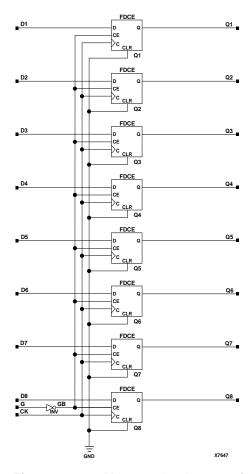

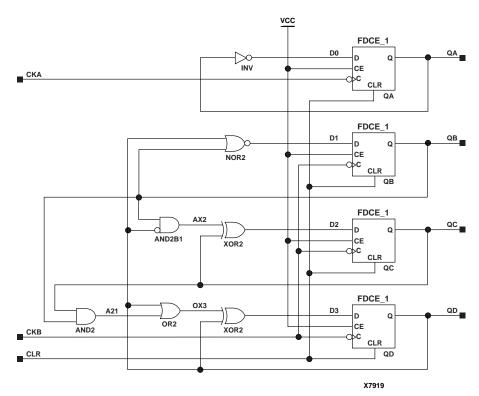

| FDCE                                                                        |      |

| D Flip-Flop with Clock Enable and Asynchronous Clear                        | 5-14 |

| FDCE_1                                                                      | 5-15 |

| D Flip-Flop with Negative-Edge Clock, Clock Enable, and Asynchronous Clear  |      |

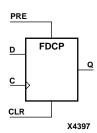

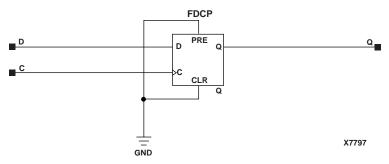

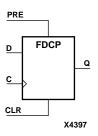

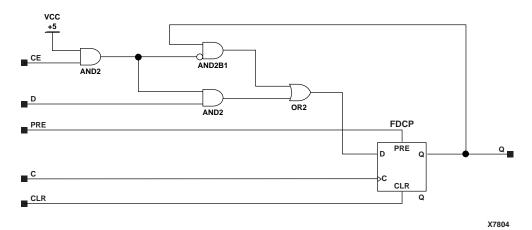

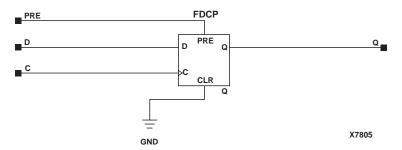

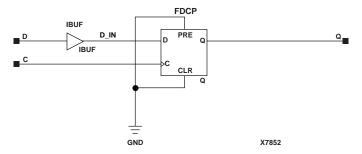

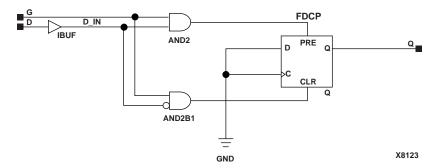

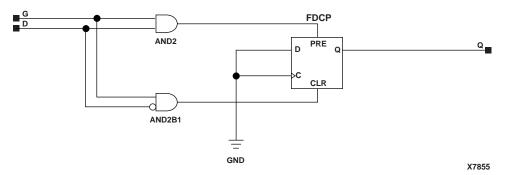

| FDCP                                                                        |      |

| D Flip-Flop Asynchronous Preset and Clear                                   |      |

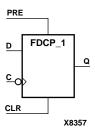

| FDCP_1                                                                      |      |

| D Flip-Flop with Negative-Edge Clock and Asynchronous Preset and Clear      |      |

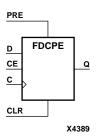

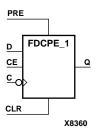

| FDCPE                                                                       |      |

| D Flip-Flop with Clock Enable and Asynchronous Preset and Clear             | 5-18 |

| FDCPE_1                                                                     | 5-19 |

| D Flip-Flop with Negative-Edge Clock, Clock Enable, and Asynchronous Preset |      |

| and Clear                                                                   | 5-19 |

| FDE                                                                         | 5-20 |

| D Flip-Flop with Clock Enable                                               |      |

| FDE_1                                                                       |      |

| D Flip-Flop with Negative-Edge Clock and Clock Enable                       |      |

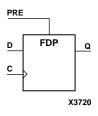

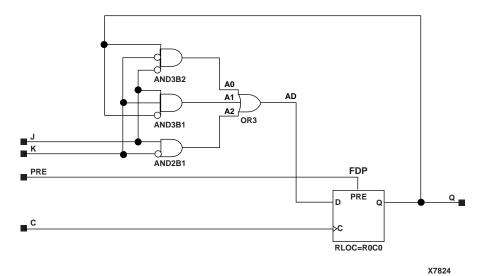

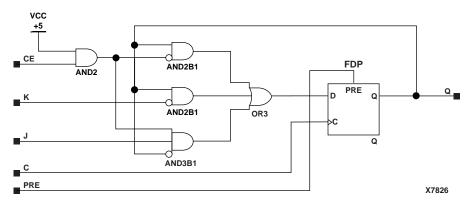

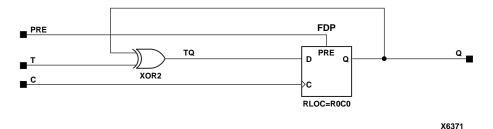

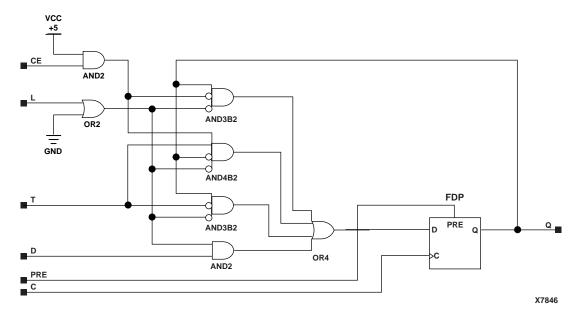

| FDP                                                                         |      |

| D Flip-Flop with Asynchronous Preset                                        |      |

| FDP_1                                                                       |      |

| D Flip-Flop with Negative-Edge Clock and Asynchronous Preset                |      |

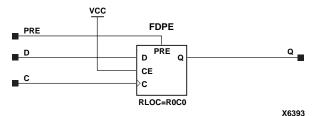

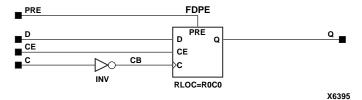

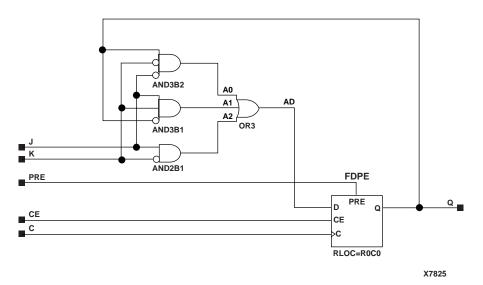

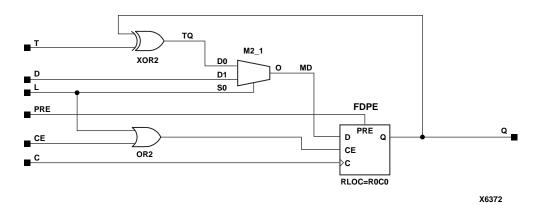

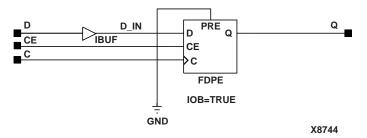

| FDPE                                                                        |      |

| D Flip-Flop with Clock Enable and Asynchronous Preset                       |      |

| FDPE_1                                                                      |      |

| D Flip-Flop with Negative-Edge Clock, Clock Enable, and Asynchronous Preset |      |

|                                                                             |      |

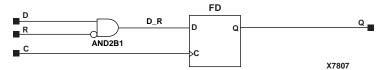

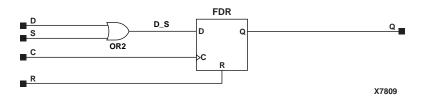

| FDR                                                                         |      |

| D Flip-Flop with Synchronous Reset                                          |      |

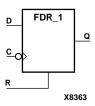

| FDR_1                                                                       |      |

| D Flip-Flop with Negative-Edge Clock and Synchronous Reset                  |      |

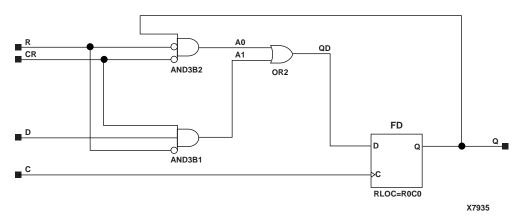

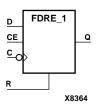

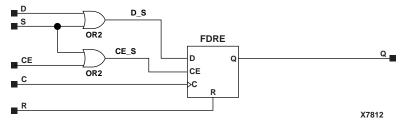

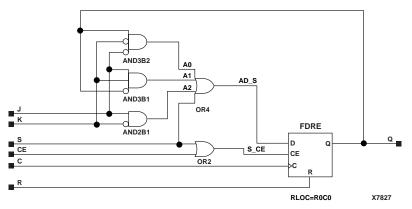

| FDRE                                                                        |      |

| D Flip-Flop with Clock Enable and Synchronous Reset                         |      |

| FDRE_1                                                                      |      |

| D Flip-Flop with Negative-Clock Edge, Clock Enable, and Synchronous Reset   | 5-30 |

Libraries Guide, 2.1i vii

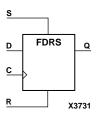

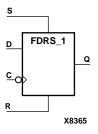

| FDRS                                                                            | 5-31 |

|---------------------------------------------------------------------------------|------|

| D Flip-Flop with Synchronous Reset and Set                                      | 5-31 |

| FDRS_1                                                                          | 5-33 |

| D Flip-Flop with Negative-Clock Edge and Synchronous Reset and Set              | 5-33 |

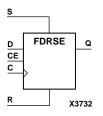

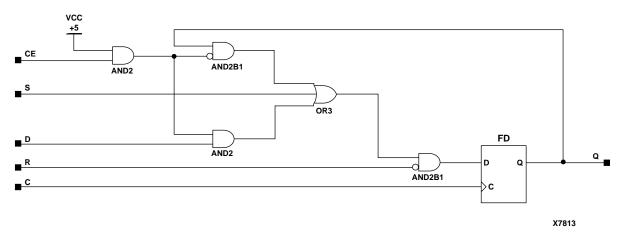

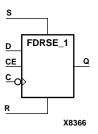

| FDRSE                                                                           | 5-34 |

| D Flip-Flop with Synchronous Reset and Set and Clock Enable                     |      |

| FDRSE 1                                                                         | 5-36 |

| D Flip-Flop with Negative-Clock Edge, Synchronous Reset and Set, and Clock      |      |

| Enable                                                                          | 5-36 |

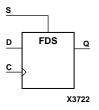

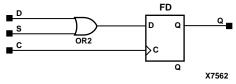

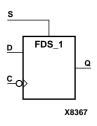

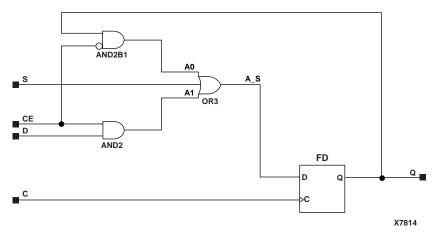

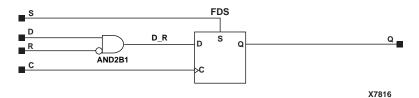

| FDS                                                                             | 5-37 |

| D Flip-Flop with Synchronous Set                                                | 5-37 |

| FDS_1                                                                           |      |

| D Flip-Flop with Negative-Edge Clock and Synchronous Set                        |      |

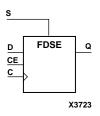

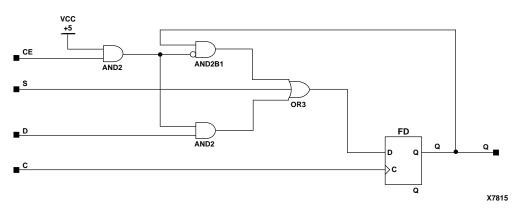

| FDSEFDSE                                                                        |      |

|                                                                                 |      |

|                                                                                 |      |

| FDSE_1                                                                          |      |

| D Flip-Flop with Negative-Edge Clock, Clock Enable, and Synchronous Set         | 5-41 |

| FDSR                                                                            | 5-42 |

| D Flip-Flop with Synchronous Set and Reset                                      | 5-42 |

| FDSRE                                                                           |      |

| D Flip-Flop with Synchronous Set and Reset and Clock Enable                     |      |

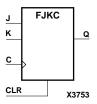

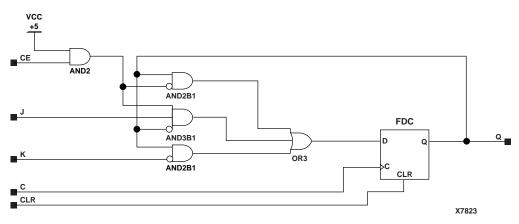

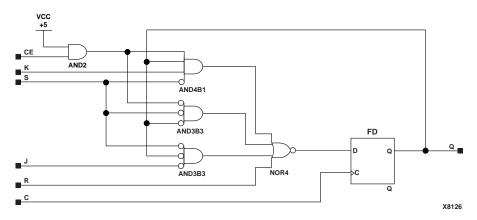

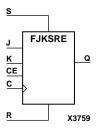

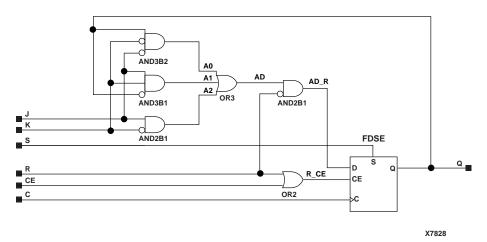

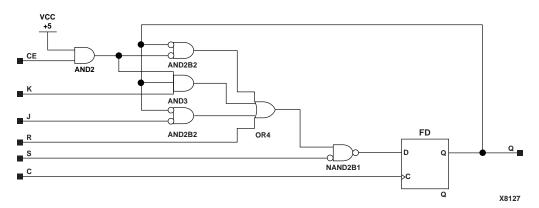

| FJKC                                                                            |      |

| J-K Flip-Flop with Asynchronous Clear                                           |      |

|                                                                                 |      |

| · · · · · · · · · · · · · · · · · · ·                                           |      |

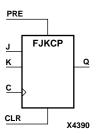

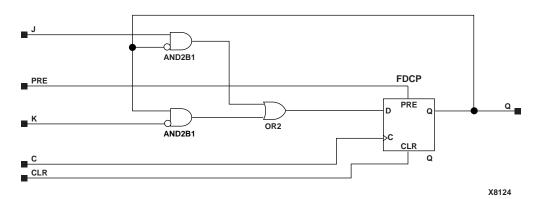

| FJKCP                                                                           |      |

| J-K Flip-Flop with Asynchronous Clear and Preset                                |      |

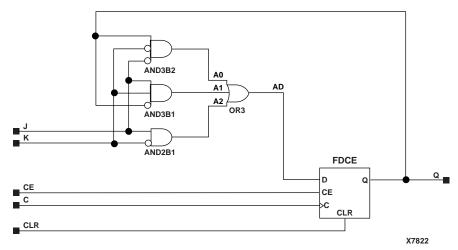

| FJKCPE                                                                          |      |

| J-K Flip-Flop with Asynchronous Clear and Preset and Clock Enable               | 5-50 |

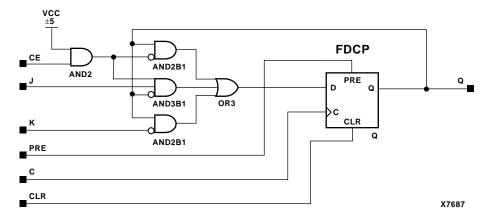

| FJKP                                                                            | 5-51 |

| J-K Flip-Flop with Asynchronous Preset                                          | 5-51 |

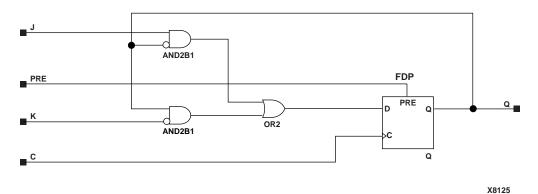

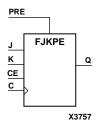

| FJKPE                                                                           | 5-53 |

| J-K Flip-Flop with Clock Enable and Asynchronous Preset                         | 5-53 |

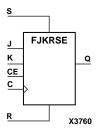

| FJKRSE                                                                          | 5-55 |

| J-K Flip-Flop with Clock Enable and Synchronous Reset and Set                   | 5-55 |

| · · · · · · · · · · · · · · · · · · ·                                           |      |

| J-K Flip-Flop with Clock Enable and Synchronous Set and Reset                   |      |

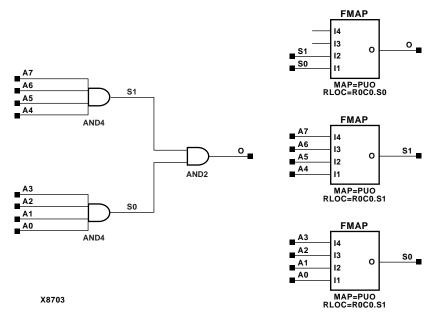

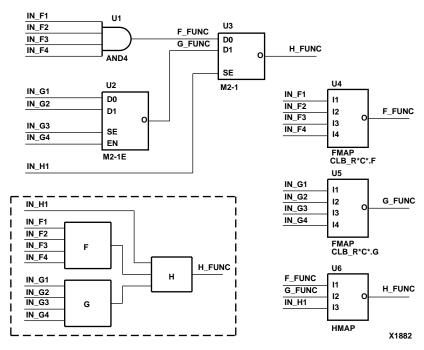

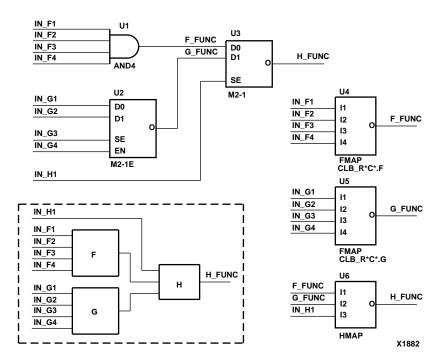

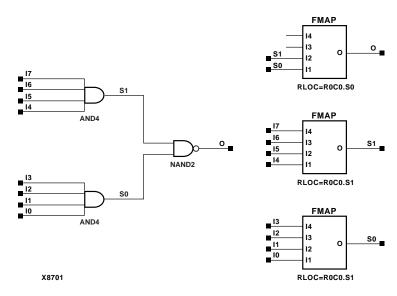

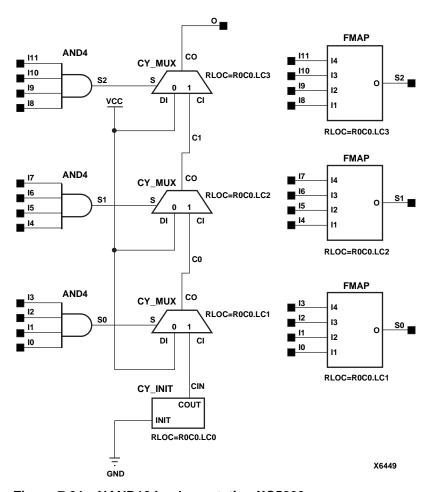

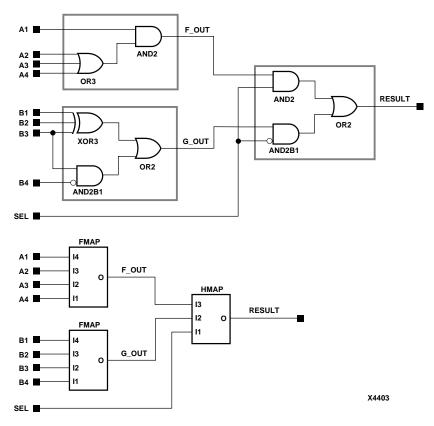

| FMAP                                                                            |      |

| F Function Generator Partitioning Control Symbol                                |      |

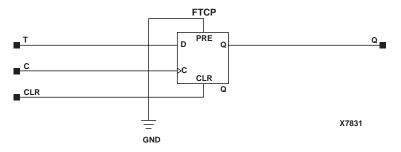

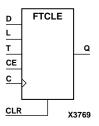

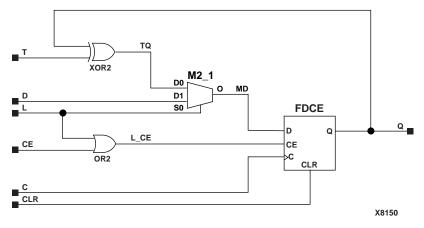

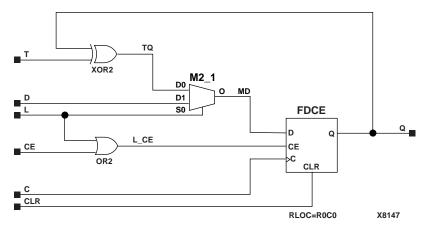

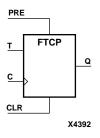

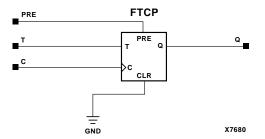

| FTC                                                                             |      |

| Toggle Flip-Flop with Toggle Enable and Asynchronous Clear                      |      |

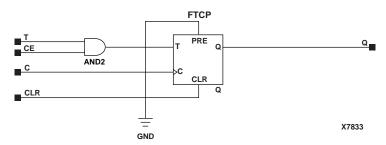

| FTCE                                                                            |      |

| Toggle Flip-Flop with Toggle and Clock Enable and Asynchronous Clear            |      |

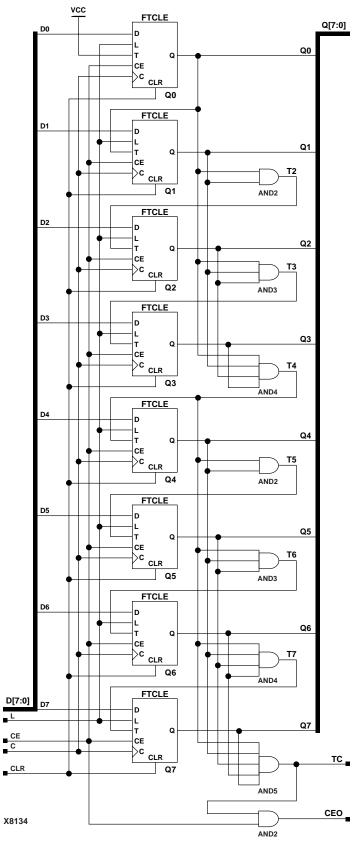

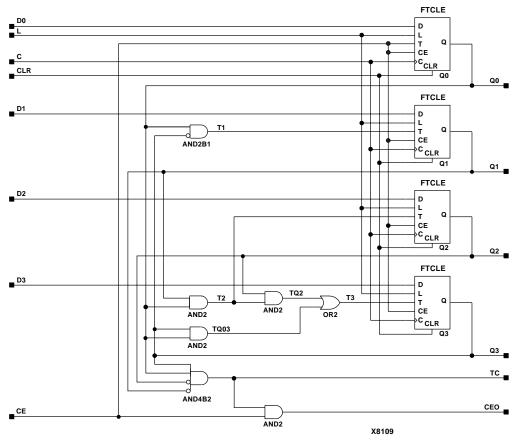

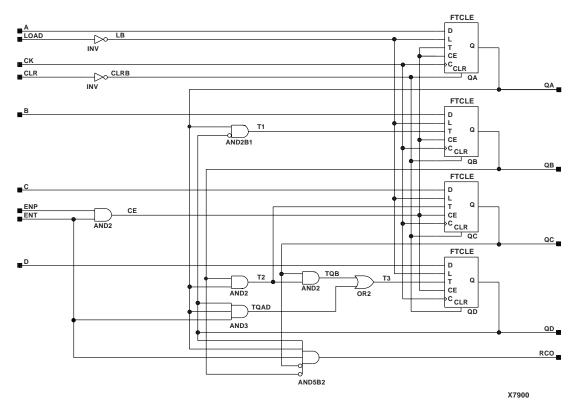

| FTCLE                                                                           |      |

| Toggle/Loadable Flip-Flop with Toggle and Clock Enable and Asynchronous Clear   |      |

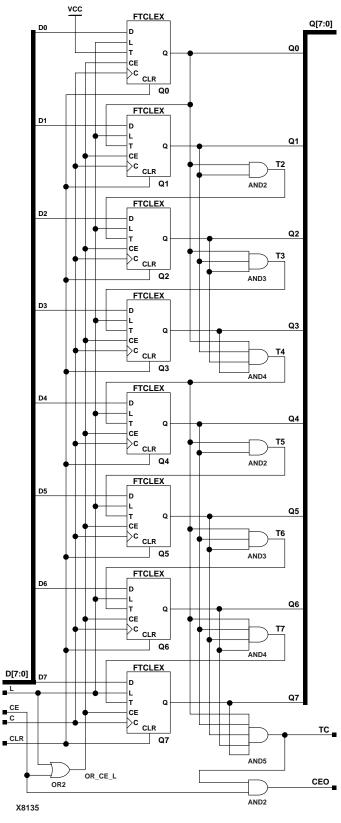

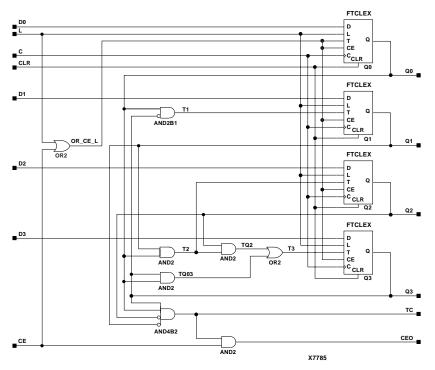

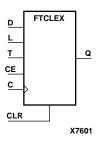

| FTCLEX                                                                          |      |

| Toggle/Loadable Flip-Flop with Toggle and Clock Enable and Asynchronous Clear   |      |

|                                                                                 |      |

| Toggle Flip Flop with Toggle English and Asynchronous Clear and Breast          |      |

| Toggle Flip-Flop with Toggle Enable and Asynchronous Clear and Preset           |      |

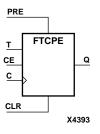

| FTCPE                                                                           |      |

| Toggle Flip-Flop with Toggle and Clock Enable and Asynchronous Clear and Preset |      |

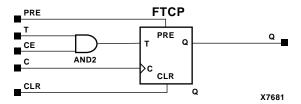

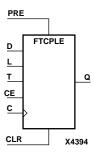

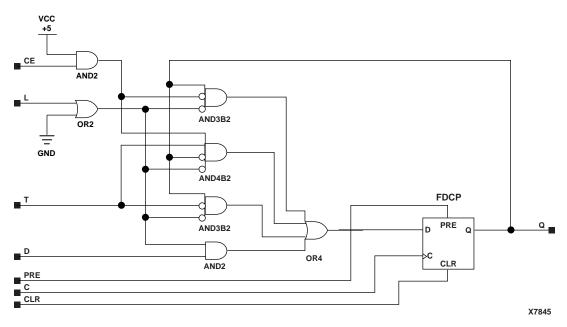

| FTCPLE                                                                          | 5-69 |

| Loadable Toggle Flip-Flop with Toggle and Clock Enable and Asynchronous         |      |

| Clear and Preset                                                                | 5-69 |

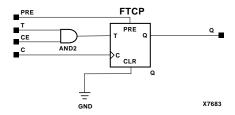

|           | FTP                                                                                   | 5-71 |

|-----------|---------------------------------------------------------------------------------------|------|

|           | Toggle Flip-Flop with Toggle Enable and Asynchronous Preset                           | 5-71 |

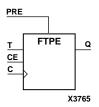

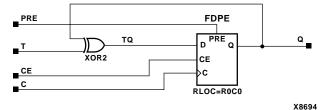

|           | FTPE                                                                                  | 5-72 |

|           | Toggle Flip-Flop with Toggle and Clock Enable and Asynchronous Preset                 |      |

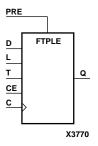

|           | FTPLE                                                                                 |      |

|           | Toggle/Loadable Flip-Flop with Toggle and Clock Enable and Asynchronous Preset FTRSE  |      |

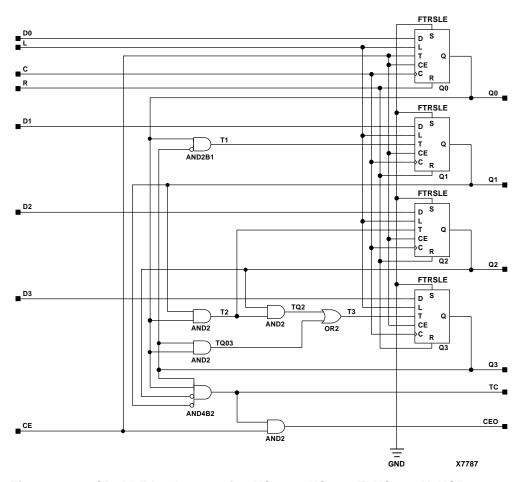

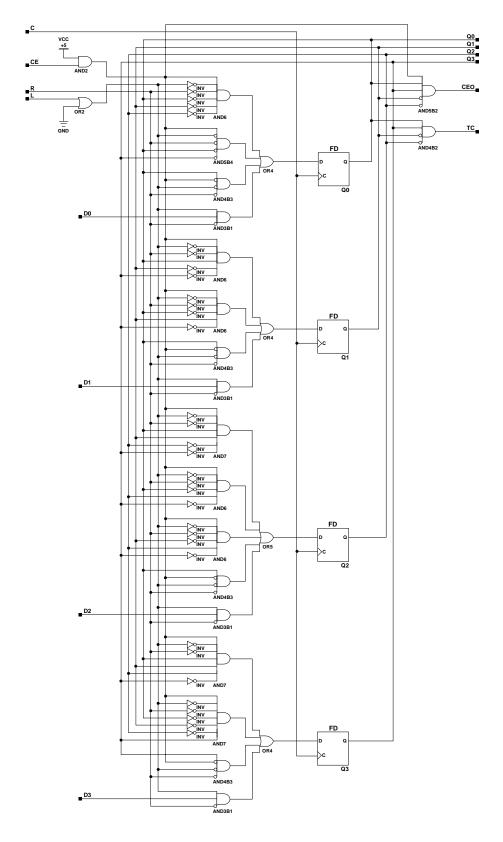

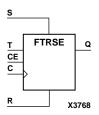

|           | Toggle Flip-Flop with Toggle and Clock Enable and Synchronous Reset and Set  FTRSLE   |      |

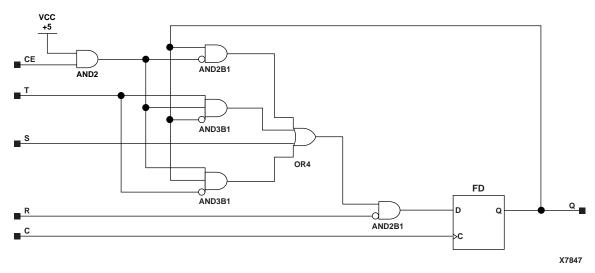

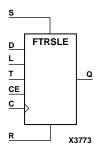

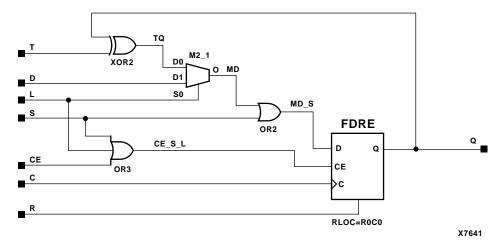

|           | Toggle/Loadable Flip-Flop with Toggle and Clock Enable and Synchronous  Reset and Set |      |

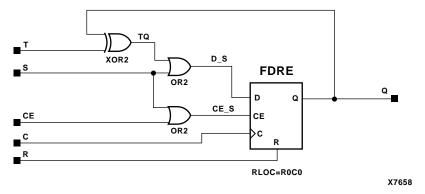

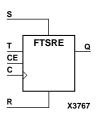

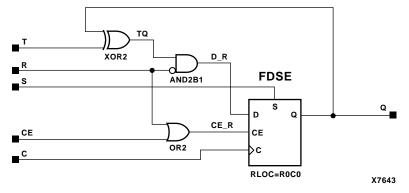

|           | FTSRE                                                                                 |      |

|           | Toggle Flip-Flop with Toggle and Clock Enable and Synchronous Set and Reset           |      |

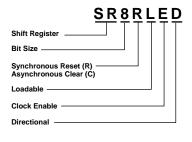

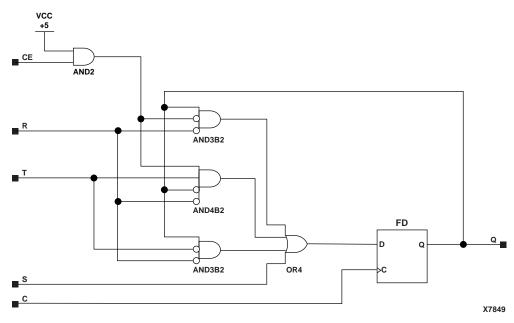

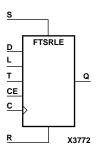

|           | FTSRLE                                                                                |      |

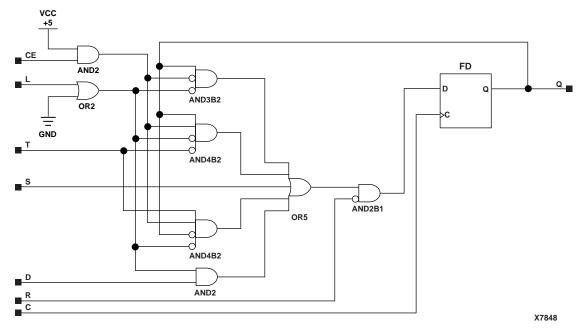

|           | Toggle/Loadable Flip-Flop with Toggle and Clock Enable and Synchronous Set and Reset  | 5-82 |

| Chapter 6 | Design Elements (GCLK to KEEPER)                                                      |      |

|           | GCLK                                                                                  | 6-2  |

|           | Global Clock Buffer                                                                   | 6-2  |

|           | GND                                                                                   | 6-3  |

|           | Ground-Connection Signal Tag                                                          |      |

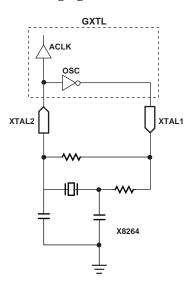

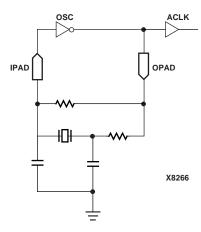

|           | GXTL                                                                                  |      |

|           | Crystal Oscillator with ACLK Buffer                                                   |      |

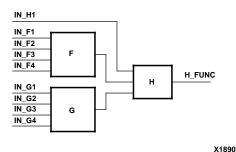

|           | HMAP                                                                                  |      |

|           | H Function Generator Partitioning Control Symbol                                      |      |

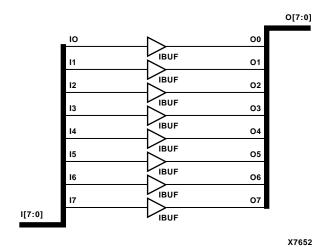

|           | IBUF, 4, 8, 16 Single- and Multiple-Input Buffers                                     |      |

|           | IBUF selectIO                                                                         |      |

|           | Single Input Buffer with Selectable I/O Interface                                     |      |

|           | IBUFG_selectIO                                                                        |      |

|           | Dedicated Input Buffer with Selectable I/O Interface                                  |      |

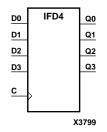

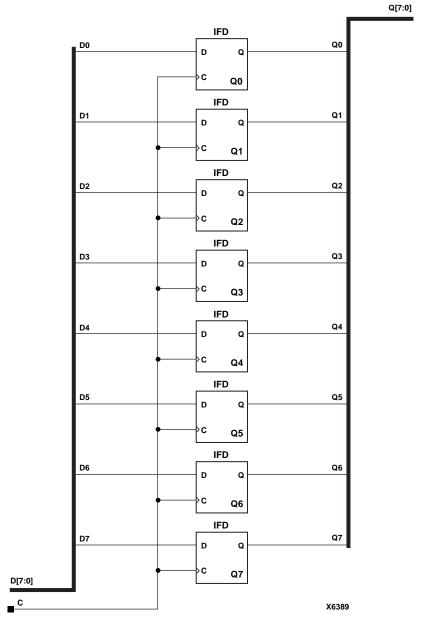

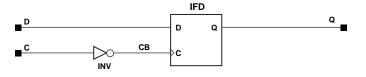

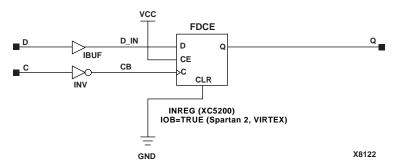

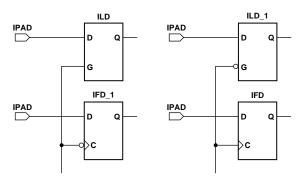

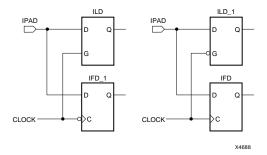

|           | IFD, 4, 8, 16                                                                         |      |

|           | Single- and Multiple-Input D Flip-Flops                                               | 6-11 |

|           | IFD_1                                                                                 |      |

|           | Input D Flip-Flop with Inverted Clock                                                 |      |

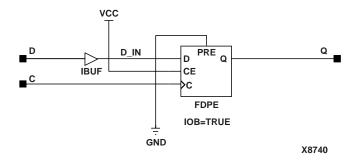

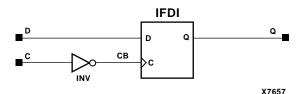

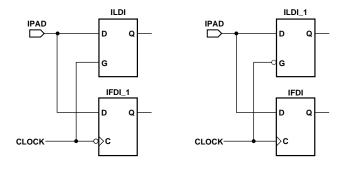

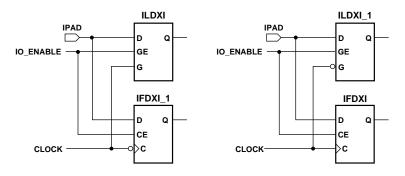

|           | IFDI                                                                                  |      |

|           | Input D Flip-Flop (Asynchronous Preset)                                               |      |

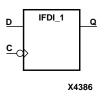

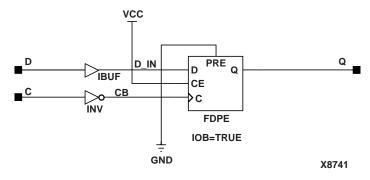

|           | IFDI_1                                                                                |      |

|           | Input D Flip-Flop with Inverted Clock (Asynchronous Preset)                           |      |

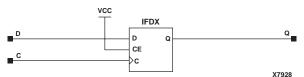

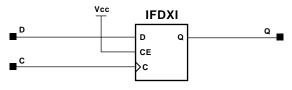

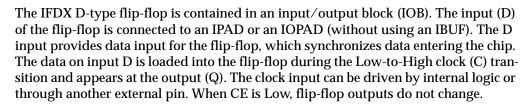

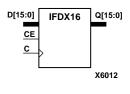

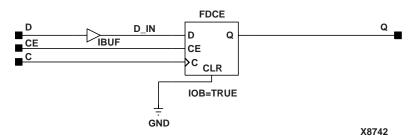

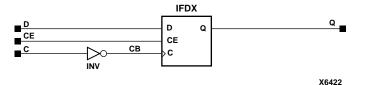

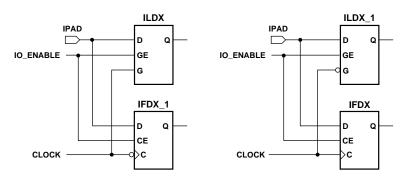

|           | Single- and Multiple-Input D Flip-Flops with Clock Enable                             |      |

|           | IFDX_1                                                                                |      |

|           | Input D Flip-Flop with Inverted Clock and Clock Enable                                |      |

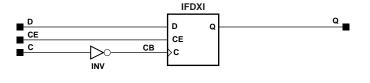

|           | IFDXI                                                                                 |      |

|           | Input D Flip-Flop with Clock Enable (Asynchronous Preset)                             |      |

|           | IFDXI_1                                                                               | 6-21 |

|           | Input D Flip-Flop with Inverted Clock and Clock Enable (Asynchronous Preset)          |      |

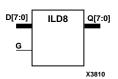

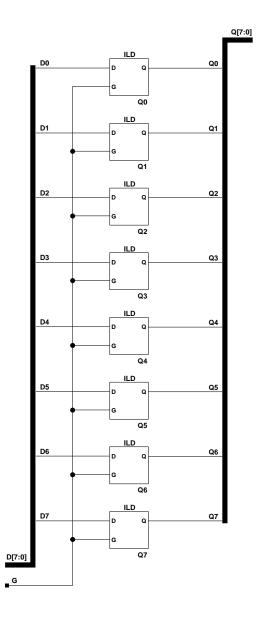

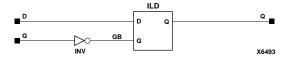

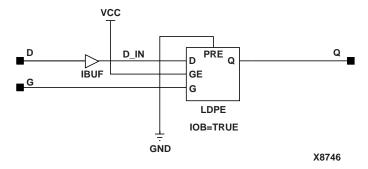

|           | ILD, 4, 8, 16                                                                         | 6-22 |

|           | Transparent Input Data Latches                                                        |      |

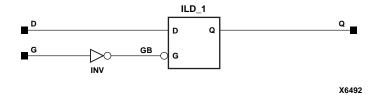

|           | ILD_1                                                                                 |      |

|           | Transparent Input Data Latch with Inverted Gate                                       |      |

|           | ILDI                                                                                  |      |

|           | Transparent Input Data Latch (Asynchronous Preset)                                    | 6-27 |

Libraries Guide, 2.1i ix

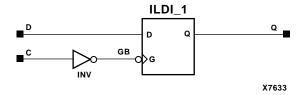

|           | ILDI_1                                                                         |        |

|-----------|--------------------------------------------------------------------------------|--------|

|           | Transparent Input Data Latch with Inverted Gate (Asynchronous Preset)          | 6-29   |

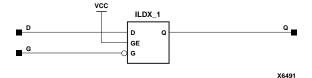

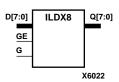

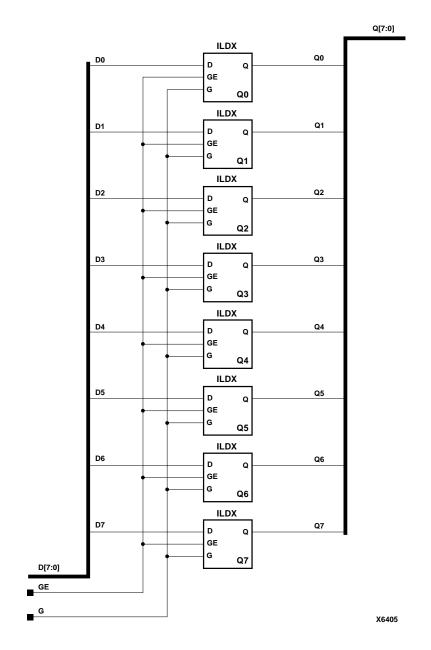

|           | ILDX, 4, 8, 16                                                                 | 6-30   |

|           | Transparent Input Data Latches                                                 | 6-30   |

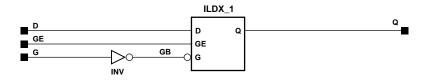

|           | ILDX_1                                                                         | 6-33   |

|           | Transparent Input Data Latch with Inverted Gate                                | 6-33   |

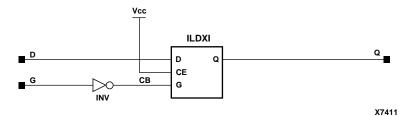

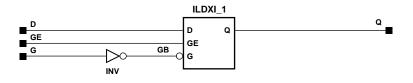

|           | ILDXI                                                                          | 6-34   |

|           | Transparent Input Data Latch (Asynchronous Preset)                             |        |

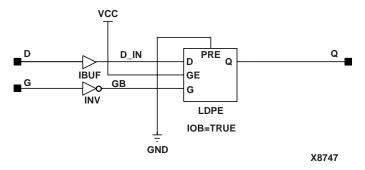

|           | ILDXI_1                                                                        |        |

|           | Transparent Input Data Latch with Inverted Gate (Asynchronous Preset)          |        |

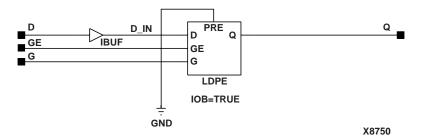

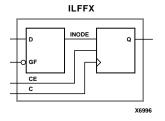

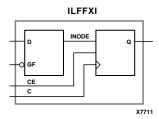

|           | ILFFX                                                                          |        |

|           | Fast Capture Input Latch                                                       |        |

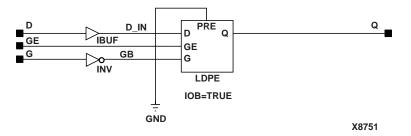

|           | ILFFXI                                                                         |        |

|           | Fast Capture Input Latch (Asynchronous Preset)                                 |        |

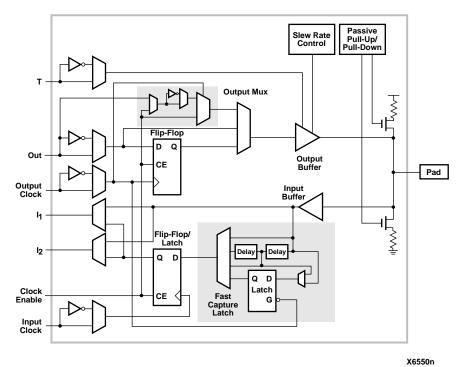

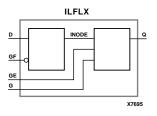

|           | ILFLX                                                                          |        |

|           | Fast Capture Transparent Input Latch                                           |        |

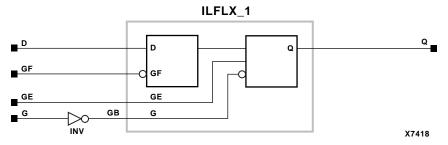

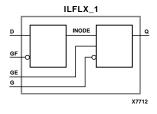

|           | ILFLX_1                                                                        |        |

|           | Fast Capture Input Latch with Inverted Gate                                    | . 6 41 |

|           |                                                                                |        |

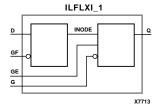

|           | ILFLXI_1                                                                       |        |

|           | Fast Capture Input Latch with Inverted Gate (Asynchronous Preset)              |        |

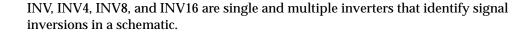

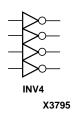

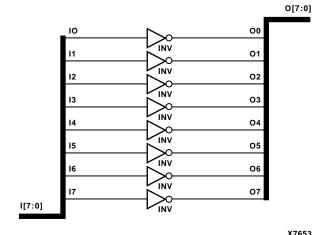

|           | INV, 4, 8, 16                                                                  |        |

|           | Single and Multiple Inverters                                                  |        |

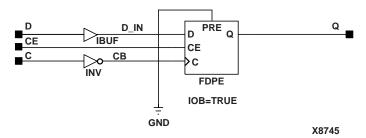

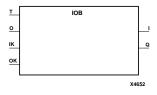

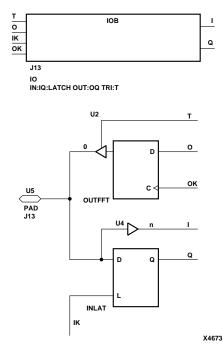

|           | IOB                                                                            |        |

|           | IOB Configuration Symbol                                                       |        |

|           | IOBUF_selectIO                                                                 |        |

|           | Bi-Directional Buffer with Selectable I/0 Interface                            |        |

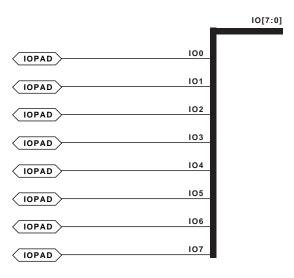

|           | IOPAD, 4, 8, 16                                                                |        |

|           | Single- and Multiple-Input/Output Pads                                         | 6-47   |

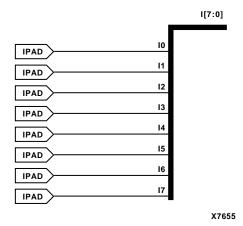

|           | IPAD, 4, 8, 16                                                                 | 6-48   |

|           | Single- and Multiple-Input Pads                                                | 6-48   |

|           | KEEPER                                                                         | 6-49   |

|           | KEEPER Symbol                                                                  | 6-49   |

| Shantar 7 | Design Florents (LD to NOD4C)                                                  |        |

| Chapter 7 | Design Elements (LD to NOR16)                                                  |        |

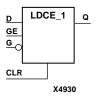

|           | LD                                                                             | . 7-2  |

|           | Transparent Data Latch                                                         |        |

|           | LD_1                                                                           |        |

|           | Transparent Data Latch with Inverted Gate                                      |        |

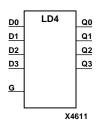

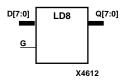

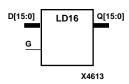

|           | LD4, 8, 16                                                                     |        |

|           | Multiple Transparent Data Latches                                              |        |

|           | LDC                                                                            |        |

|           |                                                                                |        |

|           | Transparent Data Latch with Asynchronous Clear                                 |        |

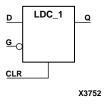

|           | LDC_1                                                                          |        |

|           | Transparent Data Latch with Asynchronous Clear and Inverted Gate               |        |

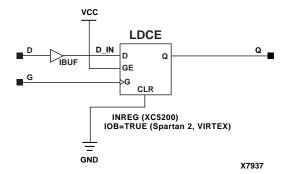

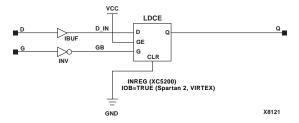

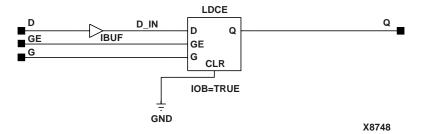

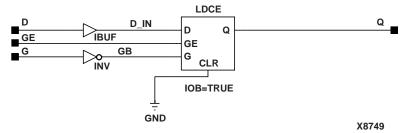

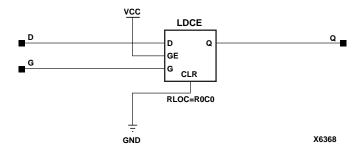

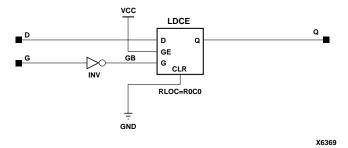

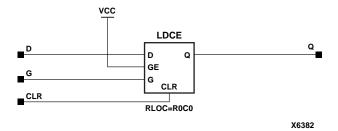

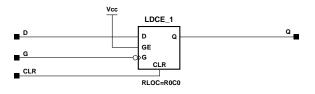

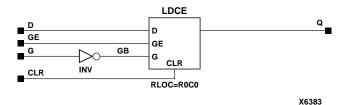

|           | LDCE                                                                           |        |

|           | Transparent Data Latch with Asynchronous Clear and Gate Enable                 |        |

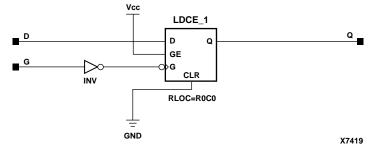

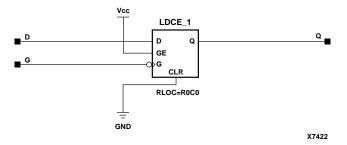

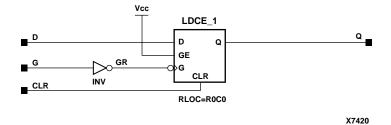

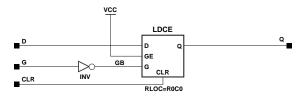

|           | LDCE_1                                                                         |        |

|           | Transparent Data Latch with Asynchronous Clear, Gate Enable, and Inverted Gate |        |

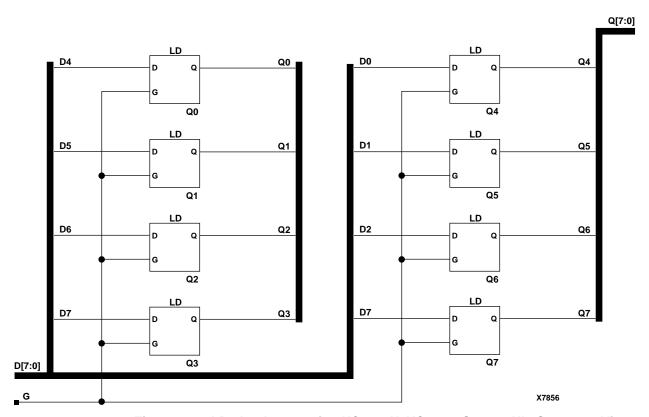

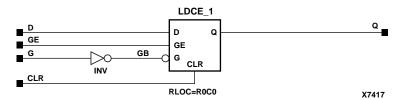

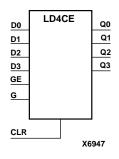

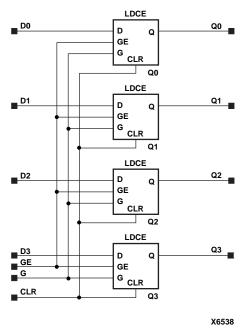

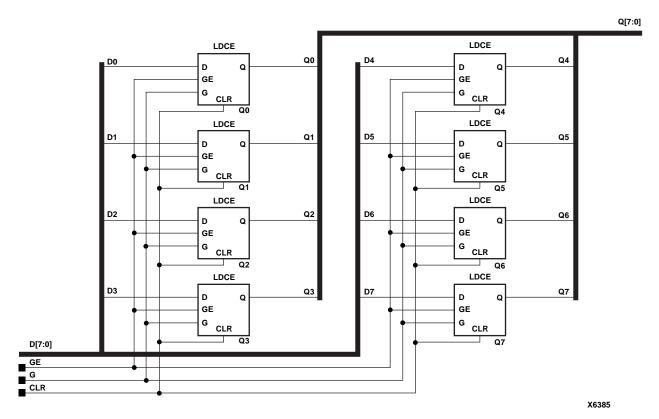

|           | LD4CE, LD8CE, LD16CE                                                           |        |

|           | Transparent Data Latches with Asynchronous Clear and Gate Enable               |        |

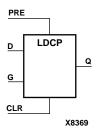

|           | LDCP                                                                           |        |

|           | Transparent Data Latch with Asynchronous Clear and Preset                      |        |

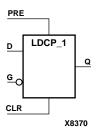

|           | LDCP_1                                                                         |        |

|           | Transparent Data Latch with Asynchronous Clear and Preset and Inverted Gate    | 7-14   |

|           |                                                                                |        |

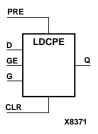

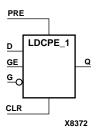

| LDCPE                                                                              | 7-15         |

|------------------------------------------------------------------------------------|--------------|

| Transparent Data Latch with Asynchronous Clear and Preset and Gate Enable  LDCPE 1 | 7-15<br>7-16 |

| Transparent Data Latch with Asynchronous Clear and Preset, Gate Enable, and        |              |

| Inverted Gate                                                                      | 7-16         |

| LDE                                                                                | 7-17         |

| Transparent Data Latch with Gate Enable                                            | 7-17<br>7-18 |

| LDE_1  Transparent Data Latch with Gate Enable and Inverted Gate                   |              |

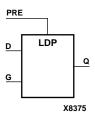

| LDP                                                                                |              |

| Transparent Data Latch with Asynchronous Preset                                    |              |

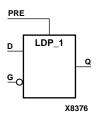

| LDP_1                                                                              |              |

| Transparent Data Latch with Asynchronous Preset and Inverted Gate                  |              |

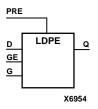

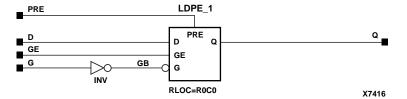

| LDPE                                                                               |              |

| Transparent Data Latch with Asynchronous Preset and Gate Enable                    | 7-21         |

| LDPE_1                                                                             |              |

| Transparent Data Latch with Asynchronous Preset, Gate Enable, and Inverted Gate    | 7-22         |

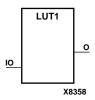

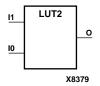

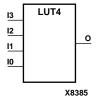

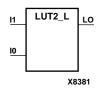

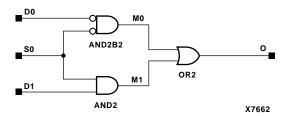

| LUT1, 2, 3, 4                                                                      |              |

| 1-, 2-, 3-, 4-Bit Look-Up-Table with General Output                                |              |

| LUT1_D, LUT2_D, LUT3_D, LUT4_D                                                     |              |

| 1-, 2-, 3-, 4-Bit Look-Up-Table with Dual Output                                   |              |

| LUT1_L, LUT2_L, LUT3_L, LUT4_L                                                     |              |

| 1-, 2-, 3-, 4-Bit Look-Up-Table with Local Output                                  |              |

| MD0                                                                                |              |

| Mode 0, Input Pad Used for Readback Trigger Input                                  |              |

| MD1                                                                                |              |

| Mode 1, Output Pad Used for Readback Data Output                                   |              |

| MD2 Mode 2, Input Pad                                                              |              |

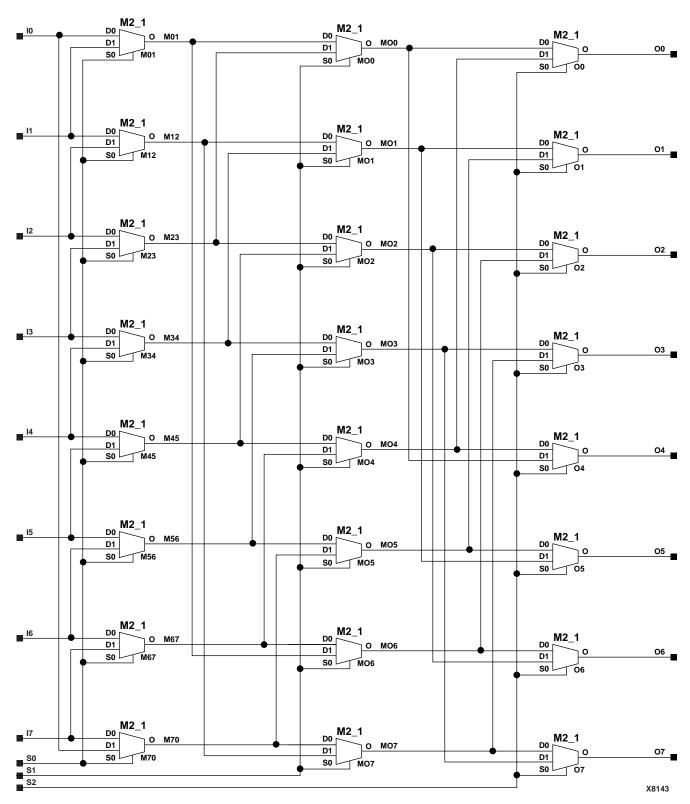

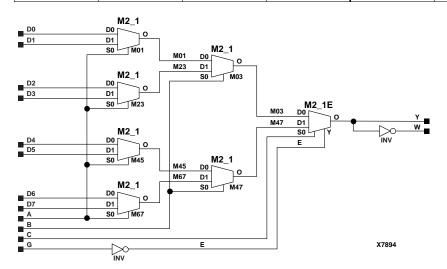

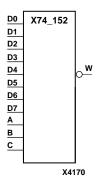

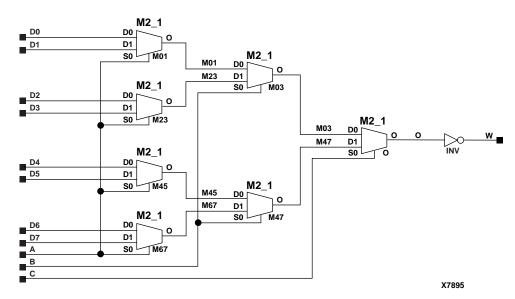

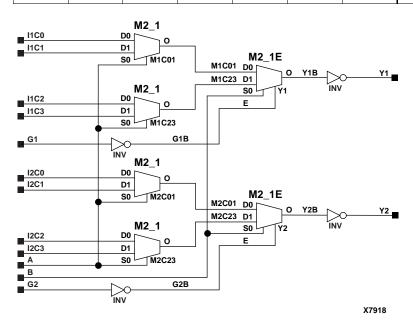

| M2_1                                                                               |              |

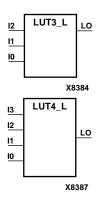

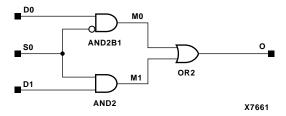

| 2-to-1 Multiplexer                                                                 |              |

| M2_1B1                                                                             |              |

| 2-to-1 Multiplexer with D0 Inverted                                                |              |

| M2_1B2                                                                             |              |

| 2-to-1 Multiplexer with D0 and D1 Inverted                                         |              |

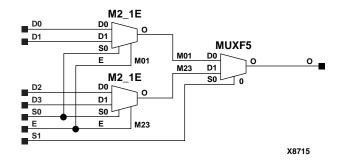

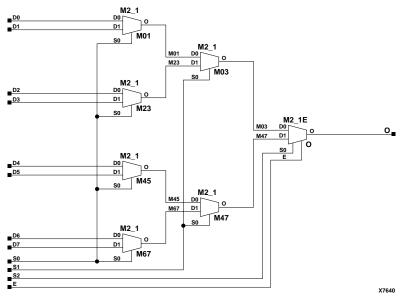

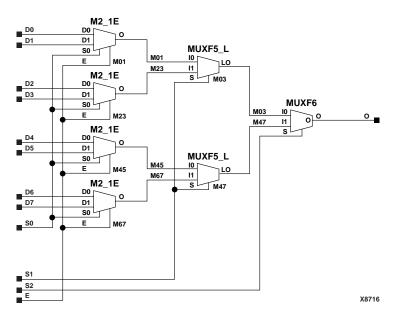

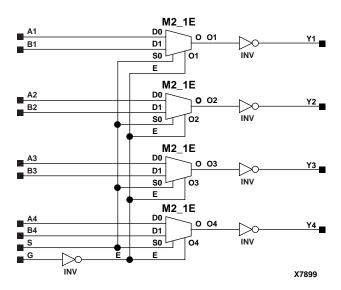

| M2_1E                                                                              |              |

| 2-to-1 Multiplexer with Enable                                                     | 7-32         |

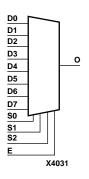

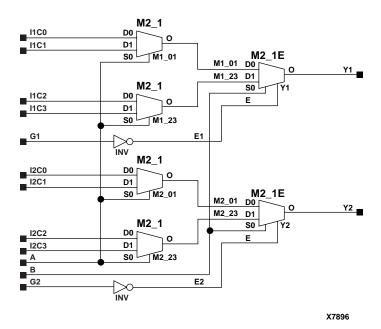

| M4_1E                                                                              |              |

| 4-to-1 Multiplexer with Enable                                                     |              |

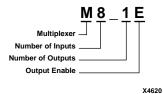

| M8_1E                                                                              |              |

| 8-to-1 Multiplexer with Enable                                                     |              |

| M16_1E                                                                             |              |

| 16-to-1 Multiplexer with Enable                                                    |              |

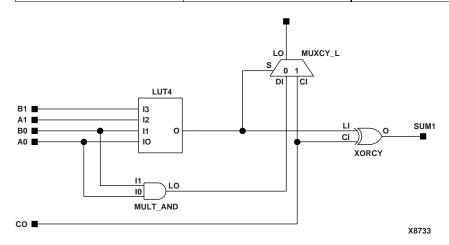

| MULT_AND                                                                           |              |

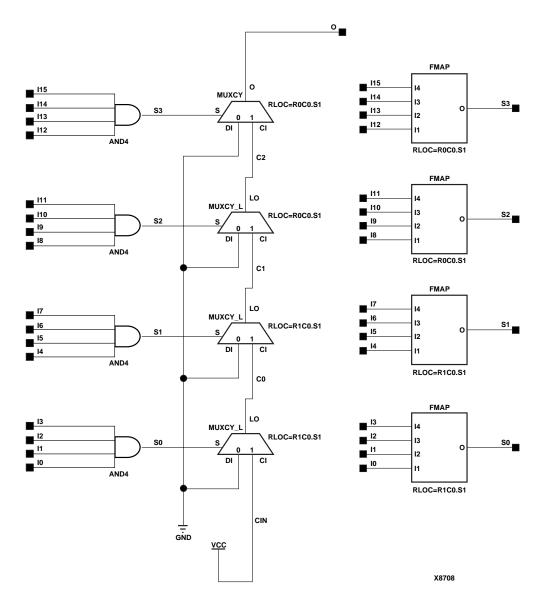

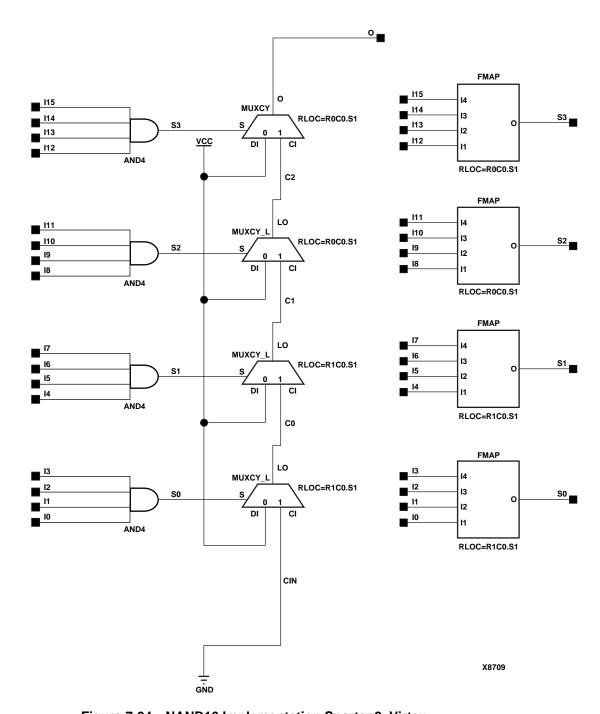

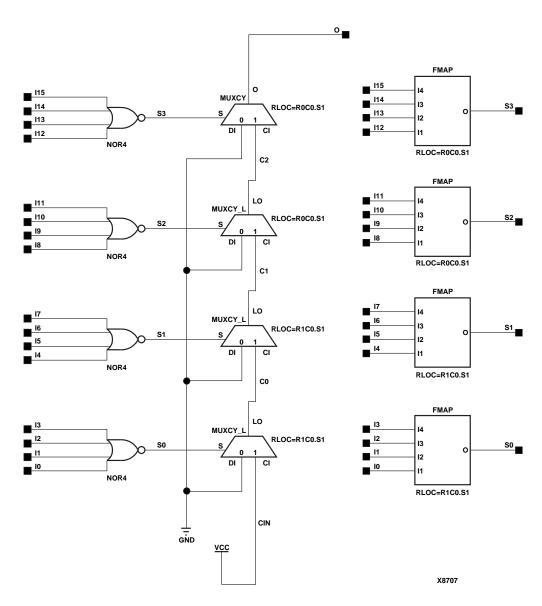

| Fast Multiplier AND MUXCY                                                          |              |

| 2-to-1 Multiplexer for Carry Logic with General Output                             |              |

| MUXCY_D                                                                            |              |

| 2-to-1 Multiplexer for Carry Logic with Dual Output                                |              |

| MUXCY_L                                                                            |              |

| 2-to-1 Multiplexer for Carry Logic with Local Output                               |              |

| MUXF5                                                                              |              |

| 2-to-1 Lookup Table Multipleyer with General Output                                | 7-41         |

Libraries Guide, 2.1i xi

|           | MUXF5_D                                                                             |      |

|-----------|-------------------------------------------------------------------------------------|------|

|           | 2-to-1 Lookup Table Multiplexer with Dual Output                                    |      |

|           | MUXF5_L                                                                             |      |

|           | 2-to-1 Lookup Table Multiplexer with Local Output                                   |      |

|           | MUXF6                                                                               |      |

|           | 2-to-1 Lookup Table Multiplexer with General Output                                 |      |

|           | MUXF6_D                                                                             |      |

|           | 2-to-1 Lookup Table Multiplexer with Dual Output                                    |      |

|           | MUXF6_L                                                                             |      |

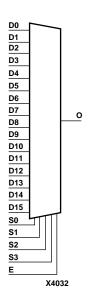

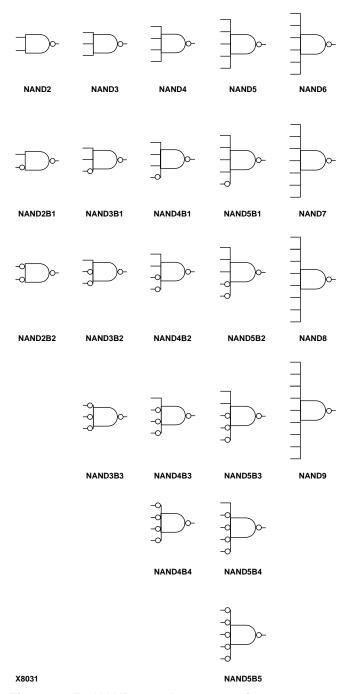

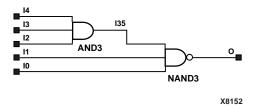

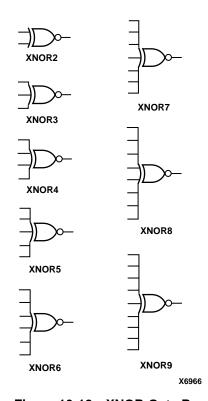

|           | 2-to-1 Lookup Table Multiplexer with Local OutputNAND2-9                            |      |

|           | 2- to 9-Input NAND Gates with Inverted and Non-Inverted Inputs                      |      |

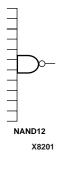

|           | NAND12, 16                                                                          |      |

|           | 12- and 16-Input NAND Gates with Non-Inverted Inputs                                |      |

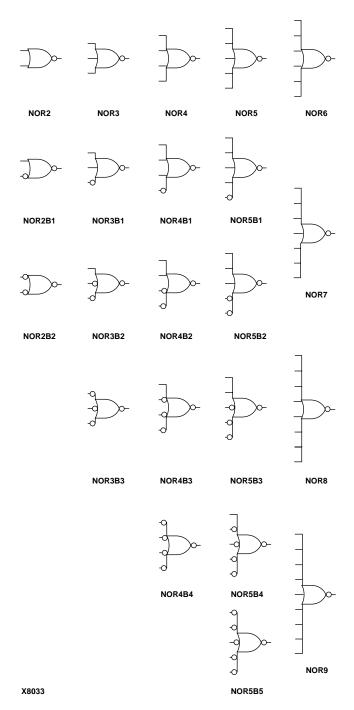

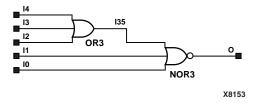

|           | NOR2-9                                                                              |      |

|           | 2- to 9-Input NOR Gates with Inverted and Non-Inverted Inputs                       |      |

|           | NOR12, 16                                                                           |      |

|           | 12- and 16-Input NOR Gates with Non-Inverted Inputs                                 |      |

| Chapter 8 | Design Elements (OAND2 to OXOR2)                                                    |      |

| Onapici o | ,                                                                                   |      |

|           | OAND2                                                                               |      |

|           | 2-Input AND Gate with Invertible Inputs                                             |      |

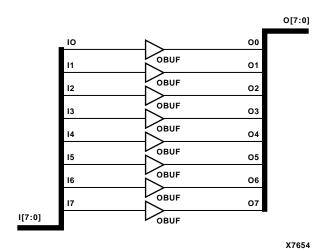

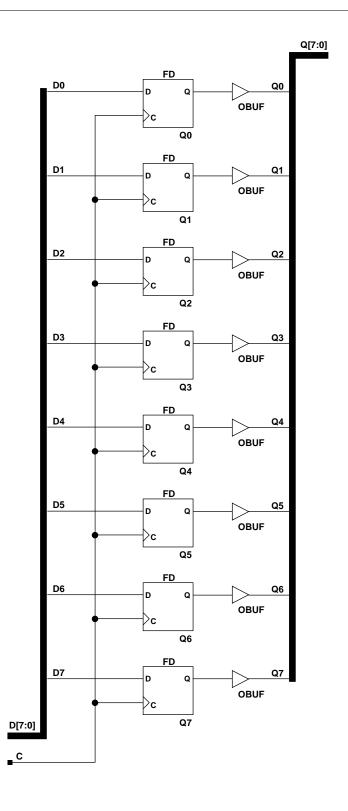

|           | OBUF, 4, 8, 16                                                                      |      |

|           | Single- and Multiple-Output Buffers  OBUF_selectIO                                  |      |

|           | Single Output Buffer with Selectable I/O Interface                                  |      |

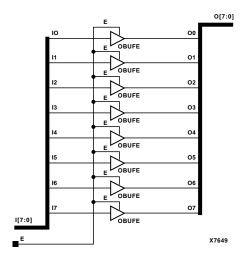

|           | OBUFE, 4, 8, 16                                                                     |      |

|           | 3-State Output Buffers with Active-High Output Enable                               |      |

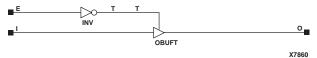

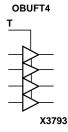

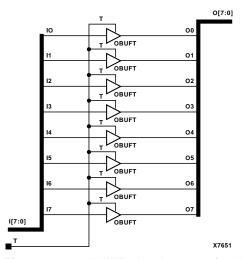

|           | OBUFT, 4, 8, 16                                                                     |      |

|           | Single and Multiple 3-State Output Buffers with Active-Low Output Enable            |      |

|           | OBUFT_selectIO                                                                      |      |

|           | Single 3-State Output Buffer with Active-Low Output Enable and Selectable           |      |

|           | I/O Interface                                                                       | 8-8  |

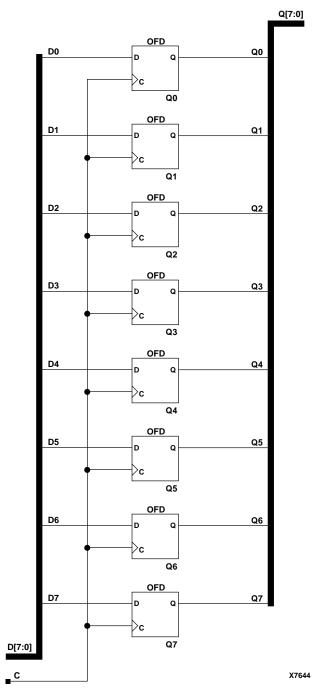

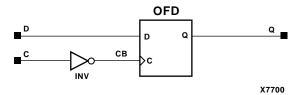

|           | OFD, 4, 8, 16                                                                       |      |

|           | Single- and Multiple-Output D Flip-Flops                                            |      |

|           | OFD_1                                                                               |      |

|           | Output D Flip-Flop with Inverted Clock                                              |      |

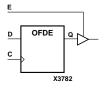

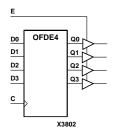

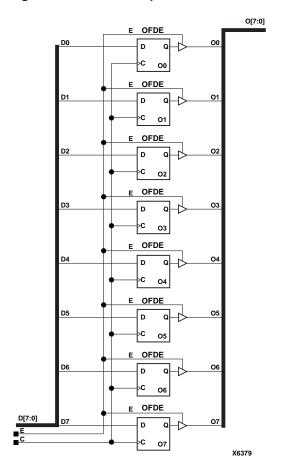

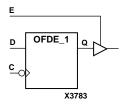

|           | OFDE, 4, 8, 16                                                                      |      |

|           | D Flip-Flops with Active-High Enable Output Buffers                                 |      |

|           | OFDE_1                                                                              |      |

|           | D Flip-Flop with Active-High Enable Output Buffer and Inverted Clock                |      |

|           | OFDEI  D Flip-Flop with Active-High Enable Output Buffer (Asynchronous Preset)      |      |

|           |                                                                                     |      |

|           | OFDEI_1  D Flip-Flop with Active-High Enable Output Buffer and Inverted Clock       | 0-19 |

|           | (Asynchronous Preset)                                                               | 0 10 |

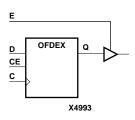

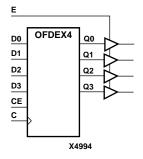

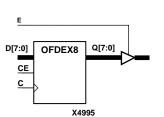

|           | OFDEX, 4, 8, 16                                                                     |      |

|           | D Flip-Flops with Active-High Enable Output Buffers and Clock Enable                |      |

|           | OFDEX_1                                                                             |      |

|           | D Flip-Flop with Active-High Enable Output Buffer, Inverted Clock, and Clock Enable |      |

|           | OFDEXI                                                                              |      |

|           | D Flip-Flop with Active-High Enable Output Buffer and Clock Enable                  |      |

|           | (Asynchronous Preset)                                                               | 8-23 |

| OFDEXI_1                                                                            | 8-24 |

|-------------------------------------------------------------------------------------|------|

| D Flip-Flop with Active-High Enable Output Buffer, Inverted Clock, and Clock Enable |      |

| (Asynchronous Preset)                                                               | 8-24 |

| OFDI                                                                                | 8-25 |

| Output D Flip-Flop (Asynchronous Preset)                                            | 8-25 |

| OFDI 1                                                                              |      |

| Output D Flip-Flop with Inverted Clock (Asynchronous Preset)                        |      |

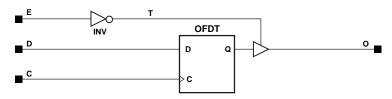

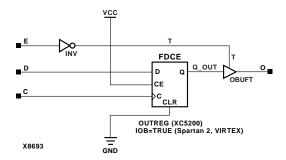

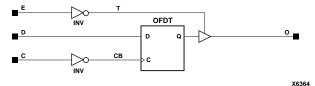

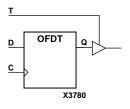

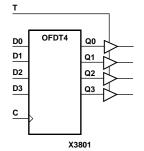

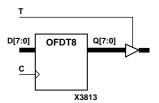

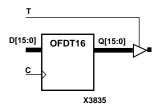

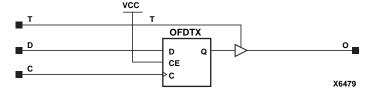

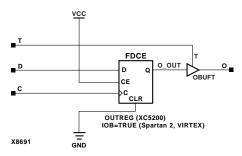

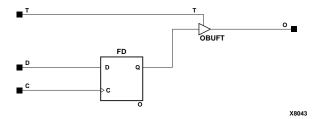

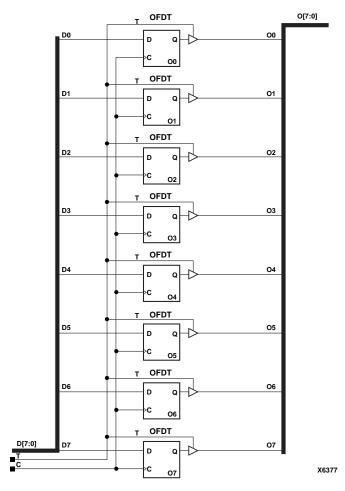

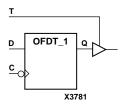

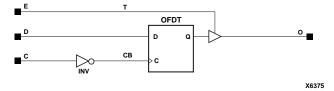

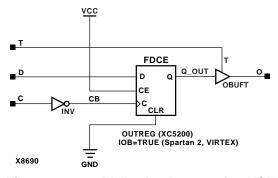

| OFDT, 4, 8, 16                                                                      |      |

| Single and Multiple D Flip-Flops with Active-Low 3-State Output Enable Buffers      |      |

| OFDT 1                                                                              |      |

| D Flip-Flop with Active-Low 3-State Output Buffer and Inverted Clock                |      |

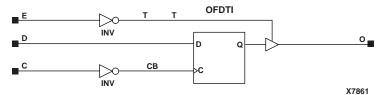

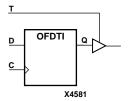

| OFDTI                                                                               |      |

| D Flip-Flop with Active-Low 3-State Output Buffer (Asynchronous Preset)             |      |

| OFDTI 1                                                                             |      |

| <del>-</del>                                                                        | 0-31 |

| D Flip-Flop with Active-Low 3-State Output Buffer and Inverted Clock                | 0.04 |

|                                                                                     | 8-31 |

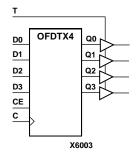

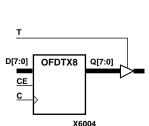

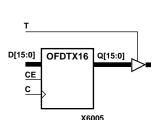

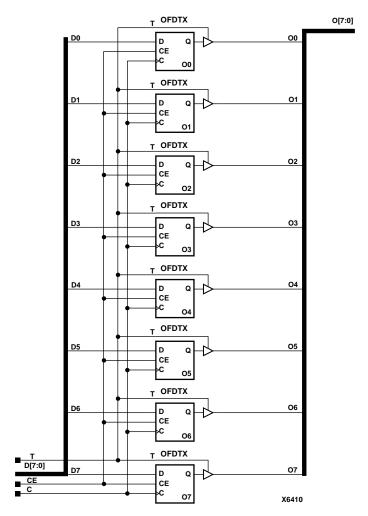

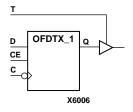

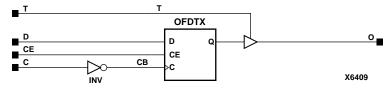

| OFDTX, 4, 8, 16                                                                     | 8-32 |

| Single and Multiple D Flip-Flops with Active-Low 3-State Output Buffers and         |      |

|                                                                                     | 8-32 |

|                                                                                     | 8-34 |

| D Flip-Flop with Active-Low 3-State Output Buffer, Inverted Clock, and Clock Enable |      |

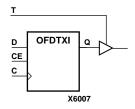

| OFDTXI                                                                              | 8-35 |

| D Flip-Flop with Active-Low 3-State Output Buffer and Clock Enable                  |      |

| (Asynchronous Preset)                                                               | 8-35 |

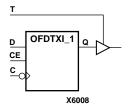

| OFDTXI_1                                                                            | 8-36 |

| D Flip-Flop with Active-Low 3-State Output Buffer, Inverted Clock, and Clock Enable |      |

| (Asynchronous Preset)                                                               | 8-36 |

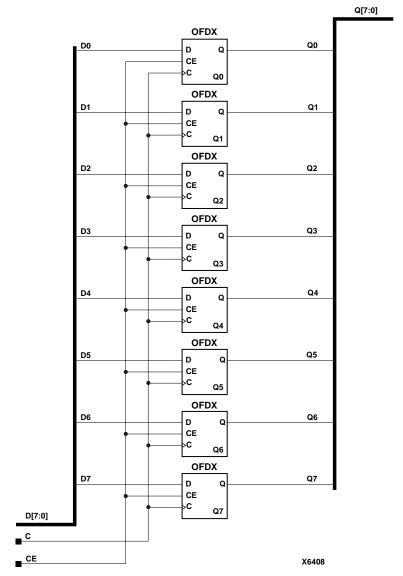

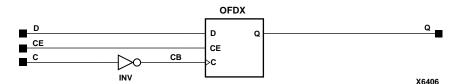

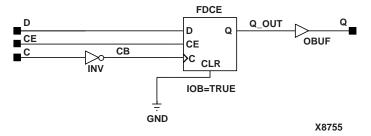

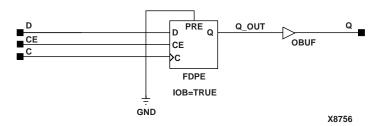

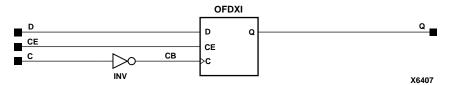

| OFDX, 4, 8, 16                                                                      | 8-37 |

| Single- and Multiple-Output D Flip-Flops with Clock Enable                          | 8-37 |

| OFDX_1                                                                              | 8-39 |

| Output D Flip-Flop with Inverted Clock and Clock Enable                             | 8-39 |

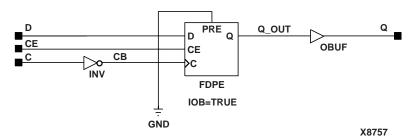

| OFDXI                                                                               |      |

| Output D Flip-Flop with Clock Enable (Asynchronous Preset)                          | 8-40 |

| OFDXI 1                                                                             |      |

| Output D Flip-Flop with Inverted Clock and Clock Enable (Asynchronous Preset)       |      |

| , , ,                                                                               | 8-42 |

| 2-to-1 Multiplexer                                                                  |      |

| ONAND2                                                                              |      |

| 2-Input NAND Gate with Invertible Inputs                                            |      |

| ONOR2                                                                               |      |

| 2-Input NOR Gate with Invertible Inputs                                             |      |

| OOR2                                                                                |      |

| 2-Input OR Gate with Invertible Inputs                                              |      |

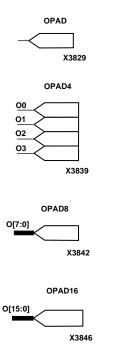

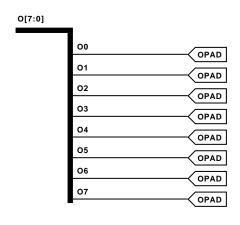

| OPAD, 4, 8, 16                                                                      |      |

| Single- and Multiple-Output Pads                                                    |      |

| · · · ·                                                                             |      |

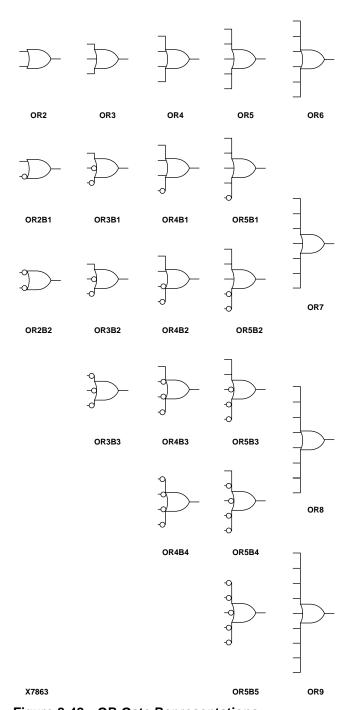

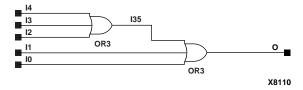

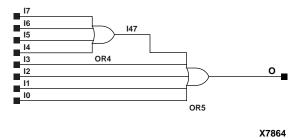

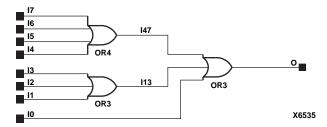

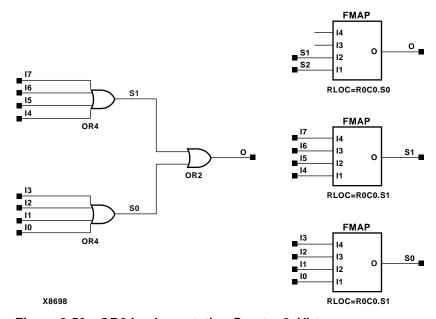

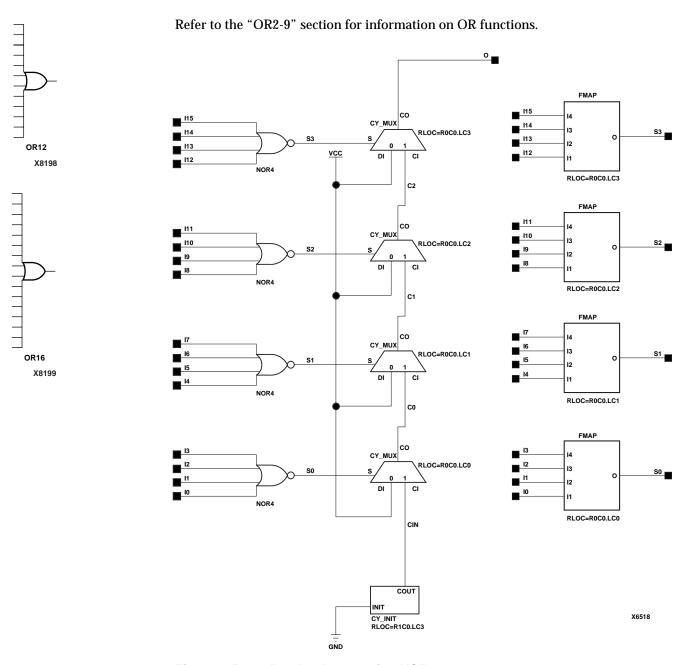

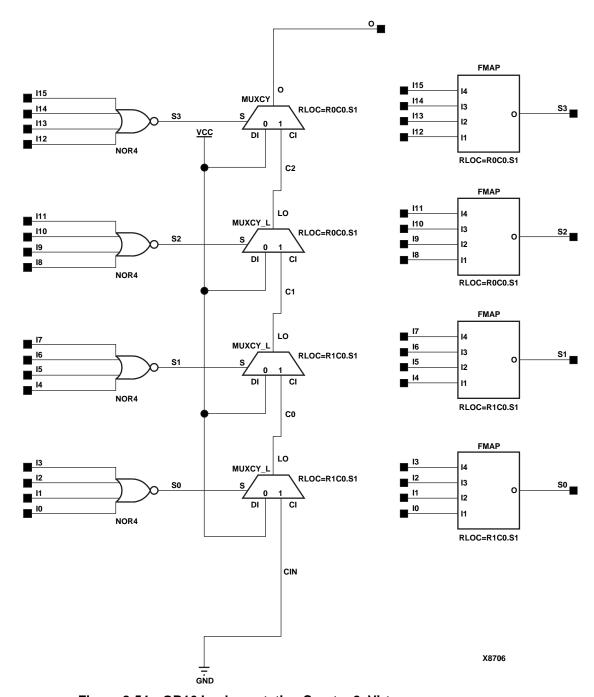

| OR2-9                                                                               |      |

| 2- to 9-Input OR Gates with Inverted and Non-Inverted Inputs                        |      |

| OR12, 16                                                                            |      |

| 12- and 16-Input OR Gates with Non-Inverted Inputs                                  |      |

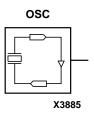

| OSC                                                                                 |      |

| Crystal Oscillator Amplifier                                                        |      |

| OSC4                                                                                |      |

| Internal 5-Frequency Clock-Signal Generator                                         | 8-53 |

Libraries Guide, 2.1i xiii

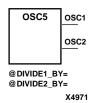

|            | OSC5                                                                        | 8-54 |

|------------|-----------------------------------------------------------------------------|------|

|            | Internal Multiple-Frequency Clock-Signal Generator                          | 8-54 |

|            | OSC52                                                                       |      |

|            | Internal Multiple-Frequency Clock-Signal Generator                          |      |

|            | OXNOR2                                                                      |      |

|            | 2-Input Exclusive-NOR Gate with Invertible Inputs                           |      |

|            | OXOR2                                                                       |      |

|            | 2-Input Exclusive-OR Gate with Invertible Inputs                            | 8-57 |

| Chapter 9  | Design Elements (PULLDOWN to ROM32X1)                                       |      |

| Jiiaptei J | ,                                                                           |      |

|            | PULLDOWN                                                                    |      |

|            | Resistor to GND for Input Pads                                              |      |

|            | PULLUP                                                                      |      |

|            | Resistor to VCC for Input PADs, Open-Drain, and 3-State Outputs             |      |

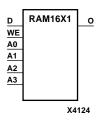

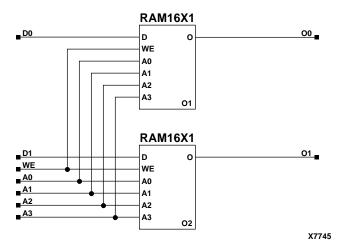

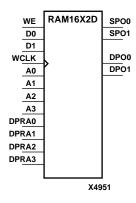

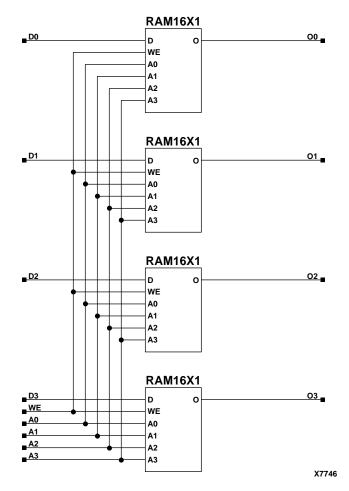

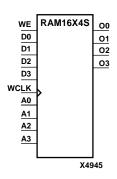

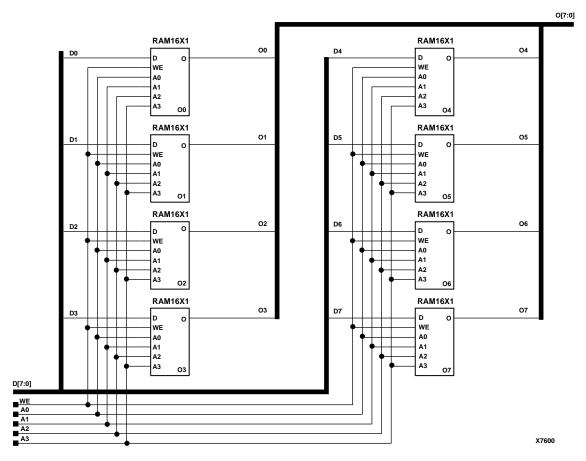

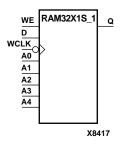

|            | RAM16X1                                                                     |      |

|            | 16-Deep by 1-Wide Static RAM                                                |      |

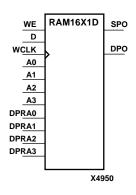

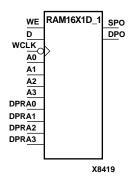

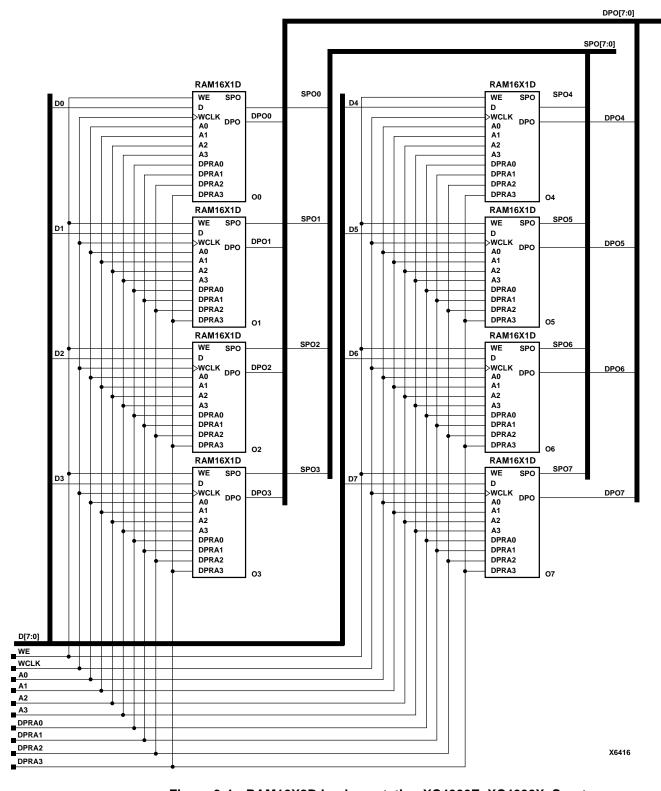

|            | RAM16X1D                                                                    |      |

|            | 16-Deep by 1-Wide Static Dual Port Synchronous RAM                          |      |

|            | RAM16X1D_1                                                                  |      |

|            | 16-Deep by 1-Wide Static Dual Port Synchronous RAM with Negative-Edge Clock |      |

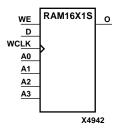

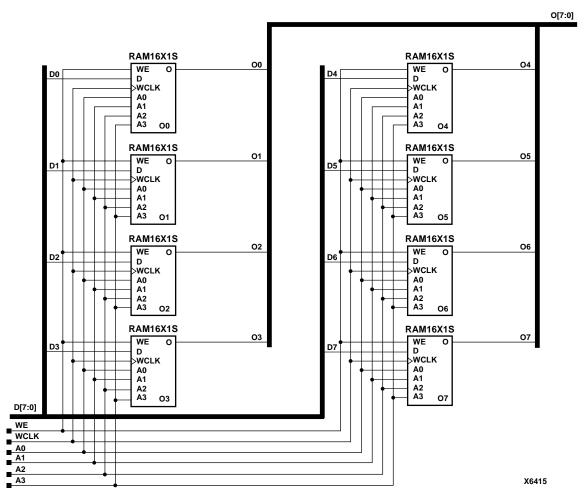

|            | RAM16X1S                                                                    |      |

|            | 16-Deep by 1-Wide Static Synchronous RAM                                    |      |

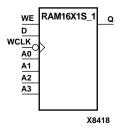

|            | RAM16X1S_1                                                                  |      |

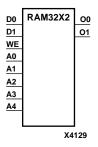

|            | RAM16X2                                                                     |      |

|            | 16-Deep by 2-Wide Static RAM                                                |      |

|            | RAM16X2D                                                                    |      |

|            | 16-Deep by 2-Wide Static Dual Port Synchronous RAM                          |      |

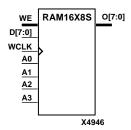

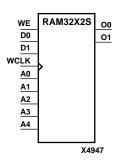

|            | RAM16X2S                                                                    |      |

|            | 16-Deep by 2-Wide Static Synchronous RAM                                    |      |

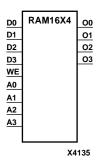

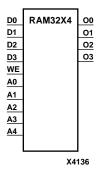

|            | RAM16X4                                                                     |      |

|            | 16-Deep by 4-Wide Static RAM                                                |      |

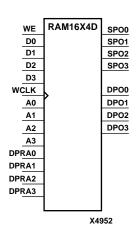

|            | RAM16X4D                                                                    |      |

|            | 16-Deep by 4-Wide Static Dual Port Synchronous RAM                          |      |

|            | RAM16X4S                                                                    | 9-15 |

|            | 16-Deep by 4-Wide Static Synchronous RAM                                    |      |

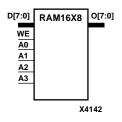

|            | RAM16X8                                                                     | 9-16 |

|            | 16-Deep by 8-Wide Static RAM                                                | 9-16 |

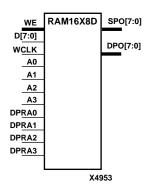

|            | RAM16X8D                                                                    | 9-18 |

|            | 16-Deep by 8-Wide Static Dual Port Synchronous RAM                          |      |

|            | RAM16X8S                                                                    |      |

|            | 16-Deep by 8-Wide Static Synchronous RAM                                    |      |

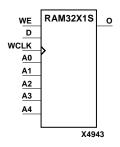

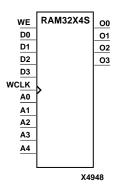

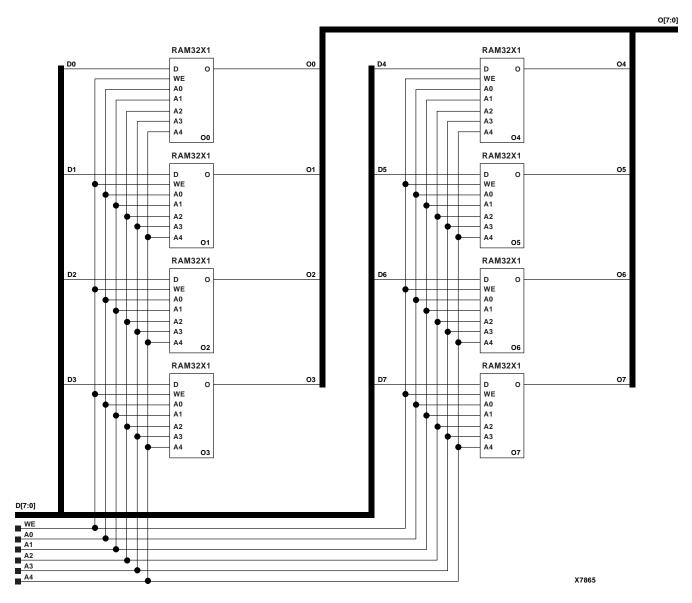

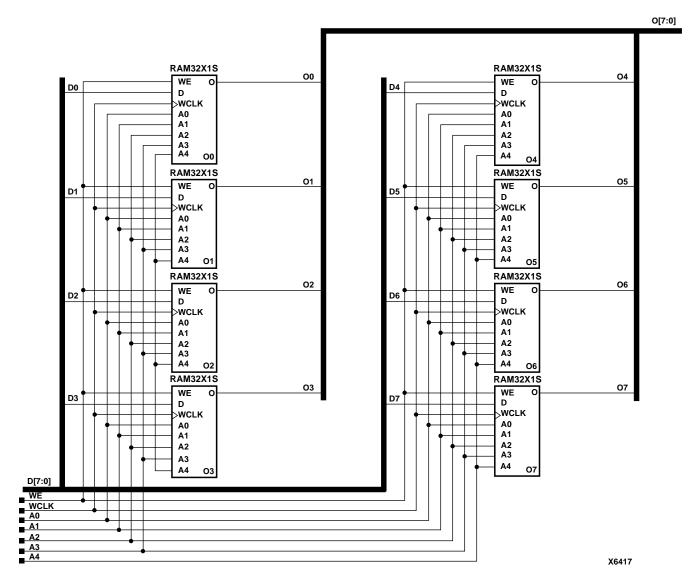

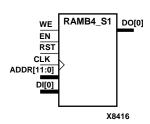

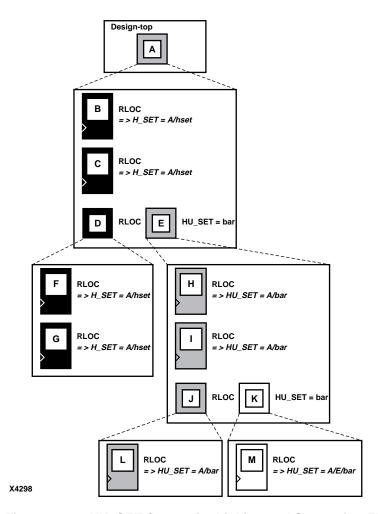

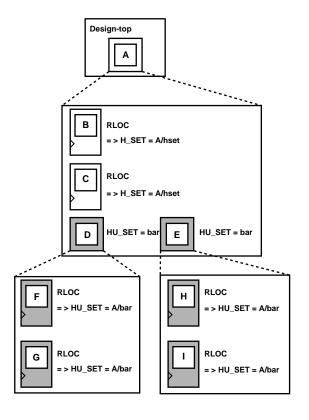

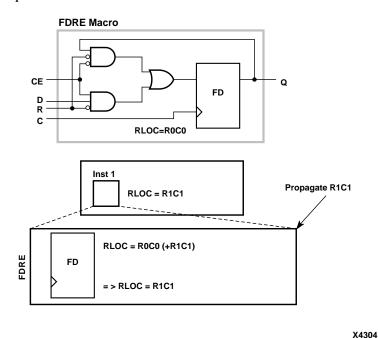

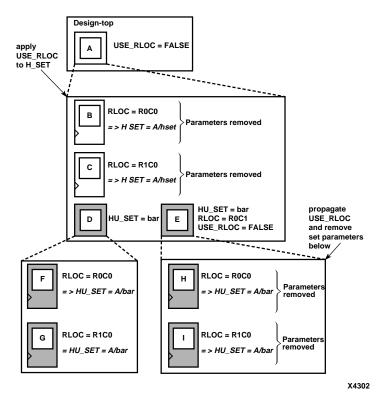

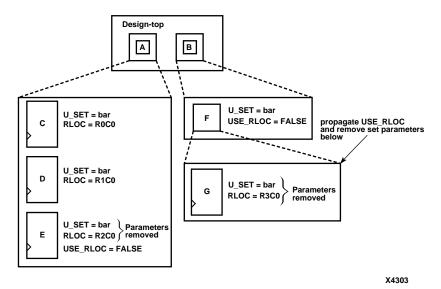

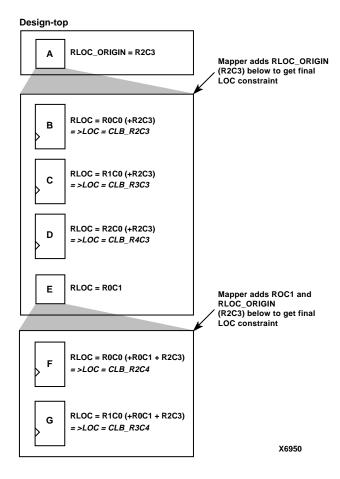

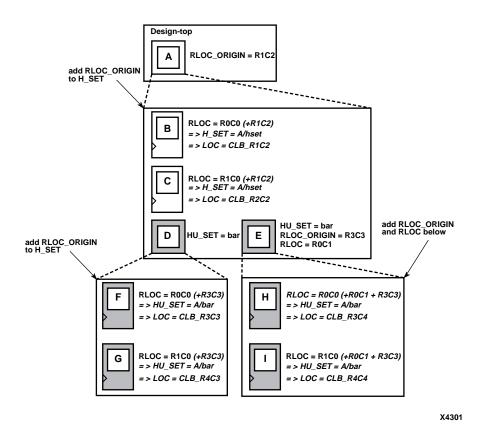

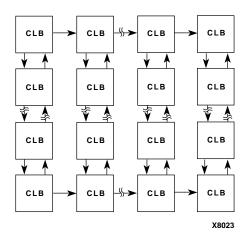

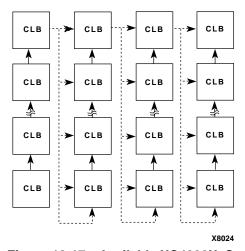

|            | RAM32X1                                                                     |      |